**Application Note**

# Astra™ Machina Foundation Series 10Base-T1S Ethernet Interface to SL16x0 SoCs

Abstract: This application note details the 10Base-T1S Ethernet interface to Astra™ Machina SL16xO series processor

### Contents

| 1. | Ove  | rview    |                                                                                  | ∠        |

|----|------|----------|----------------------------------------------------------------------------------|----------|

|    | 1.1. | Scope    | eT1S Ethernet (IEEE 802.3cg)                                                     | <u>/</u> |

|    | 1.2. | 1.2.1.   | Hardware Interface with SL1640 and SL1680 SoCsHardware MDI Bus Interface Network | 6        |

| 2. | Refe |          | Trandware Met Dus Interface Network                                              |          |

| 3. | Revi | sion His | tory                                                                             |          |

Oomloaded by Anothrous Oos and State of Social State of Social

# List of Figures

| Figure 1. 10Base-T1S Ethernet PHY Hardware Connection to SL1620 SoC            | 5 |

|--------------------------------------------------------------------------------|---|

| Figure 2. 10Base-T1S Ethernet PHY Hardware Connection to SL1640 and SL1680 SoC |   |

| Figure 3. MDI Bus Interface Network for 10Base-T1S Communication               |   |

### 1. Overview

The Synaptics SL16xO SoC family features embedded processors with native AI acceleration, designed for multi-modal applications in consumer and industrial IoT. These SoCs incorporate dedicated hardware accelerators for machine learning, security, graphics, and multimedia, optimizing performance for AI inference, secure processing, and media workloads. As part of Synaptics' Astra platform, the SL16xO series combines high-performance computing capabilities with robust connectivity options and AI development tools, enabling seamless deployment.

10Base-T1S Ethernet, standardized under IEEE 802.3cg, is a cost-effective, single-pair Ethernet technology designed for short-range (up to 25 meters) networking in industrial, automotive, and IoT environments. Operating at 10 Mbps over a single twisted pair, it supports a multi-drop topology, allowing up to eight devices to share a cable segment while eliminating the need for a switch. Its Physical Layer Collision Avoidance (PLCA) mechanism ensures deterministic, collision-free communication, making it ideal for low-power, short-distance applications where simplified cabling and reliability are critical.

### 1.1. Scope

This document provides an in-depth analysis of the hardware integration and interoperability between 10Base-T1S Ethernet (IEEE 802.3cg) devices and Synaptics' SL16xO SoC family. It details the implementation of 10Base-T1S Ethernet for low-power, single-pair networking and how it complements the Al-driven processing and connectivity features of the SL16xO SoC. The document highlights key design considerations, performance optimizations, and real-world application scenarios, demonstrating how this combination enables efficient, scalable, and cost-effective solutions for industrial automation, IoT deployments, and smart building infrastructure.

## 1.2. 10Base-T1S Ethernet (IEEE 802.3cg)

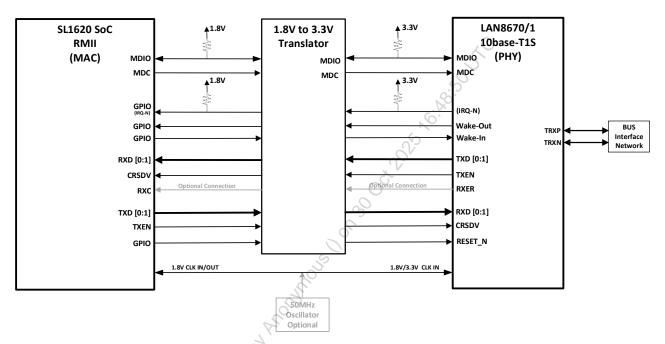

The SL1620 SoC supports RGMII and RMII Ethernet interfaces, enabling seamless integration with 10Base-T1S Ethernet devices and ICs, as illustrated in Figure 1.

The bus interface network topology can be configured as either multi-drop or point-to-point, depending on application requirements. The SL1620 provides a 50MHz RMII reference clock (1.8V) for external PHY interfaces, while the LAN8670/1 PHY supports both 1.8V or 3.3V reference clocks.

The RXER/RXC (Receive Error) connection is optional. Additionally, the SL1620's GPIOs (1.8V/3.3V) can be configured for interrupt and wake control signals as needed.

Figure 1. 10Base-T1S Ethernet PHY Hardware Connection to SL1620 SoC

#### 1.2.1. Hardware Interface with SL1640 and SL1680 SoCs

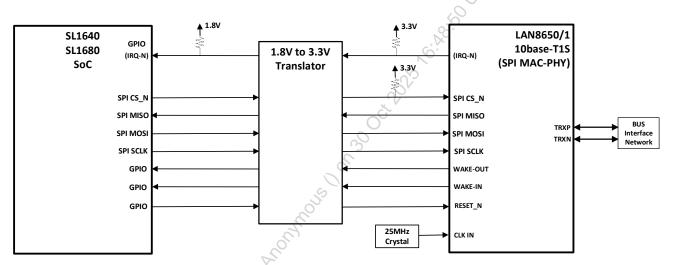

The SL1640 SoC includes an integrated Fast Ethernet MAC-PHY, enabling direct Ethernet connectivity without an external PHY. In contrast, the SL1680 SoC features a Gigabit Ethernet MAC but supports only an RGMII interface, requiring an external PHY for network connectivity.

To enable 10Base-T1S Ethernet on these SoCs, an SPI-based MAC-PHY solution is necessary, providing seamless communication over a single twisted pair while ensuring compliance with the IEEE 802.3cg standard.

The bus interface network can be configured in either a multi-drop topology, allowing multiple devices to share a single cable segment without a switch, or a point-to-point connection for a dedicated link between two nodes. This flexibility supports optimized network architectures for industrial, IoT, and automation applications, where cost-effective, low-power, and deterministic communication is essential.

Figure 2. 10Base-T1S Ethernet PHY Hardware Connection to SL1640 and SL1680 SoC

#### 1.2.2. Hardware MDI Bus Interface Network

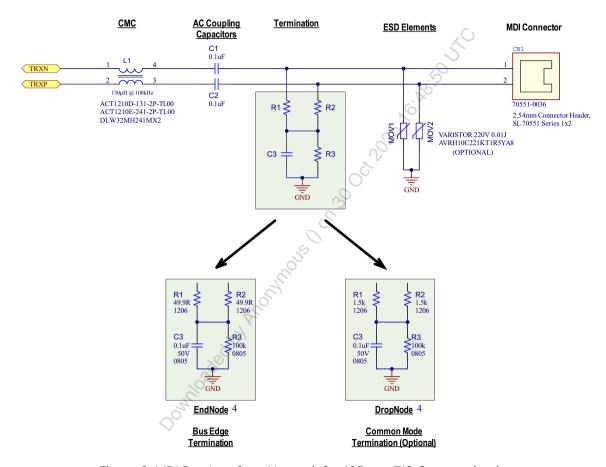

Figure 3 illustrates the 10Base-T1S multi-drop topology, which allows multiple devices to share a single twisted pair, reducing costs and simplifying network infrastructure by eliminating the need for switches. This topology ensures reliable communication in industrial, IoT, and automation applications.

Additionally, the Optimized BIN enhances system robustness and electromagnetic compatibility (EMC), improving resistance to noise, signal degradation, and environmental interference. This resilience is particularly valuable in industrial environments, where maintaining signal integrity and minimizing electromagnetic interference (EMI) are critical for stable and deterministic data transmission.

Figure 3. MDI Bus Interface Network for 10Base-T1S Communication

7

# 2. References

- SL1620 Embedded IOT Processor Electrical Specification Datasheet (PN: 505-001428-01)

- SL1640 Embedded IOT Processor Electrical Specification Datasheet (PN: 505-001415-01)

- SL1680 Embedded IOT Processor Electrical Specification Datasheet (PN: 505-001413-01)

- Microchip LNA8670/1 10BASE-T1S Ethernet PHY Transceiver Product Brief https://ww1.microchip.com/downloads/en/DeviceDoc/PB-LAN8670-1-2-60001536E.pdf

- Microchip LAN8650/1 10BASE-T1S MAC-PHY Ethernet Controller with SPI Datasheet https://ww1.microchip.com/downloads/aemDocuments/documents/AIS/ProductDocuments/DataSheets/LAN8650-1-Data-Sheet-60001734.pdf

# 3. Revision History

| Revision | Description      |

|----------|------------------|

| Α        | Initial release. |

Domina ded by Annymous On 30 Cet. 20th No. As. So. Unicode do by Annymous On 30 Cet. 20th No. As. So. Unicode do by Annymous On 30 Cet. 20th No. As. So. As. S

#### Copyrigh

Copyright © 2025 Synaptics Incorporated. All Rights Reserved.

#### Trademark

Astra Machina, Synaptics and the Synaptics logo are trademarks or registered trademarks of Synaptics Incorporated in the United States and/or other countries.

All other trademarks are the properties of their respective owners.

#### Contact U

Visit our website at www.synaptics.com to locate the Synaptics office nearest you. PN: 506-001610-01 Rev A

#### Notice

Use of the materials may require a license of intellectual property from a third party or from Synaptics. This document conveys no express or implied licenses to any intellectual property rights belonging to Synaptics or any other party. Synaptics may, from time to time and at its sole option, update the information contained in this document without notice.

INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED "AS-IS," AND SYNAPTICS HEREBY DISCLAIMS ALL EXPRESS OR IMPLIED WARRANTIES, INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, AND ANY WARRANTIES OF NON-INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT SHALL SYNAPTICS BE LIABLE FOR ANY DIRECT, INCIDENTAL, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES ARISING OUT OF OR IN CONNECTION WITH THE USE OF THE INFORMATION CONTAINED IN THIS DOCUMENT, NEWEYER CAUSED AND BASED ON ANY THEORY OF LIABILITY, WHETHER IN AN ACTION OF CONTRACT, NEGLIGENCE OR OTHER TORTIOUS ACTION, AND EVEN IF SYNAPTICS WAS ADVISED OF THE POSSIBILITY OF SUCH DAMAGE. IF A TRIBUNAL OF COMPETENT JURISDICTION DOES NOT PERMIT THE DISCLAIMER OF DIRECT DAMAGES OR ANY OTHER DAMAGES, SYNAPTICS' TOTAL CUMULATIVE LIABILITY TO ANY PARTY SHALL NOT EXCEED ONE HUNDRED US. DOLLARS.