**Application Note**

# Astra™ Machina Foundation Series eMMC Configuration

Abstract: This application note provides detailed guidelines for connecting and configuring the eMMC with the SL1620, SL1640, SL1680 and SL2610 RDK.

## Contents

| 1. | Ove   | rview                                    | 5  |

|----|-------|------------------------------------------|----|

|    | 1.1.  | Scope                                    | 5  |

|    | 1.2.  | Hardware Connection of eMMC on Astra RDK | 6  |

|    |       | 1.2.1. Power supply of eMMC              | 6  |

|    |       | 1.2.2. Resistors/Capacitor on eMMC Bus   | 6  |

|    |       | 1.2.3. VDDI Capacitor                    | 6  |

|    | 1.3.  | eMMC Boot mode                           | 7  |

|    | 1.4.  | Internal Pull-Up resistors Control       | 8  |

|    | 1.5.  | Delay-Line Tuning                        | 8  |

|    |       | 1.5.1. Read Tuning                       | 8  |

|    |       | 1.5.2. Write Tuning                      | 8  |

|    | 1.6.  | PCB Layout Guidelines                    | 9  |

| 2. | Refe  | erences                                  | 10 |

| ۲٠ | 11010 |                                          |    |

| 3  | Revi  | sion History                             | 11 |

# List of Figures

| Figure 1. Overview of Astra Machina Foundation Series | 5 |

|-------------------------------------------------------|---|

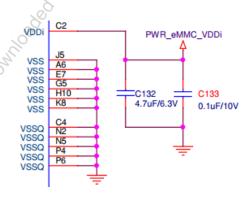

| Figure 2. Capacitors on VDDI                          | 6 |

| Figure 3. Boot mode of Astra Machina processor        | 7 |

Download Dy Andrina Oct. 2012 Processes of the State of t

# List of Tables

| Table 1. eMMC Speed Modes supported by Astra Machina RDKRDK | 5 |

|-------------------------------------------------------------|---|

| Table 2. eMMC pin assignment with Voltage                   | 6 |

| Table 3. eMMC Internal Pull-Up/Dn resistor register         | 8 |

| Table 4. eMMC CLK TXDLY register                            | 8 |

| Table 5. eMMC CLK TXDLY Recommended Setting                 | 9 |

Downloaded by Anonymous On Social Property of the Social Property of

# 1. Overview

The Astra Machina RDK (Reference Development Kit) is a versatile development platform for embedded system applications. It is equipped with a high-performance processor and a suite of peripherals to accelerate system prototyping and development. This application note provides detailed guidance on integrating and using an eMMC device with the Astra Machina RDK platform.

### 1.1. Scope

This document is intended for developers using the Astra Machina RDK platform to prototype systems that require eMMC for storage and boot. It provides detailed design recommendations, hardware design, and troubleshooting tips to ensure proper eMMC operation.

Figure 1. Overview of Astra Machina Foundation Series

The Astra Machina RDK platform supports an integrated eMMC controller compliant with JEDEC eMMC 5.1 specifications. Summary of eMMC Speed Modes:

Table 1. eMMC Speed Modes supported by Astra Machina RDK

| Mode        | Bus Speed | Bus Widths          | Clock Frequency | I/O Voltage |  |

|-------------|-----------|---------------------|-----------------|-------------|--|

| Legacy Mode | 25MB/s    | 1-bit, 4-bit, 8-bit | 25MHz           | 1.8V        |  |

| High-Speed  | 50MB/s    | 1-bit, 4-bit, 8-bit | 50MHz           | 1.8V        |  |

| DDR52       | 100MB/s   | 4-bit, 8-bit        | 50MHz           | 1.8V        |  |

| HS200 (SDR) | 200MB/s   | 4-bit, 8-bit        | 200MHz          | 1.8V        |  |

| HS400 (DDR) | 400MB/s   | 8-bit               | 200MHz          | 1.8V        |  |

#### 1.2. Hardware Connection of eMMC on Astra RDK

#### 1.2.1. Power supply of eMMC

The Astra Machina series SoC supports a fixed 1.8V I/O signaling voltage for eMMC. The eMMC power supply requirements.

Table 2. eMMC pin assignment with Voltage

| Name Voltage |      | Description                |  |  |

|--------------|------|----------------------------|--|--|

| VCC          | 3.3V | Power supply for EMMC CORE |  |  |

| VCCQ         | 1.8V | Power supply for I/O       |  |  |

#### 1.2.2. Resistors/Capacitor on eMMC Bus

- **Pull-Up resistors:** The SL16xO eMMC controller includes internal pull-up resistors for the CMD and DATA[7:0] signals. Therefore, no external pull-up resistors are required.

- Pull-Down resistors:

- $\circ$  Connect the eMMC RSTn signal to GND through a 4.7 k $\Omega$  resistor.

- o Connect the eMMC STRB signal to GND through a 47 k $\Omega$  resistor.

- Series resistors:

- $\circ$  Place a 22  $\Omega$  or 33  $\Omega$  series resistor on the eMMC CLK and eMMC STRB signals.

- o Series resistors are not required on other eMMC signals.

- Capacitor: Place a 0.1 µF capacitor on the eMMC RSTn pin

#### 1.2.3. VDDI Capacitor

To prevent voltage fluctuations on the **VDDI** pin, it is recommended to place a combination of **4.7**  $\mu$ F and **0.1**  $\mu$ F decoupling capacitors in parallel.

Figure 2. Capacitors on VDDI

#### 1.3. eMMC Boot mode

The Astra Machina RDK platform is typically designed to support **eMMC Boot Mode** as defined by the JEDEC eMMC standard. Boot mode allows the system to directly load the bootloader (or firmware) from the eMMC's boot partitions, making it a common and reliable method for embedded system initialization.

To boot from the eMMC device, both the Astra Machina **processor** and the **eMMC device** must be properly configured in **eMMC Boot Mode**.

SL16x0 Boot Strap pin: Configure Boot\_SRC[1:0] pins to 2'b10 for eMMC Boot mode.

| BootS | rc[1:0]        | TYPE                       |   |

|-------|----------------|----------------------------|---|

|       | 2'b00          | SPI-Secure Boot            |   |

|       | 2'b01          | ROM boot from NAND default | 0 |

|       | 2 <b>'</b> b10 | ROM boot from EMMC         | ) |

|       | 2'b11          | SPI-Clear Boot             |   |

|       |                |                            |   |

• SL261x Boot Strap pin: Configure Boot\_SRC[1:0] pins to 2'b10 for eMMC Boot mode too.

| BootSrc[1:0] | TYPE O                     |

|--------------|----------------------------|

| 2'b00        | ROM boot from USB2         |

| 2'b01        | ROM boot from xSPI_NOR     |

| 2'b10        | ROM boot from EMMC default |

| 2'b11        | ROM boot from xSPI_NAND    |

Figure 3. Boot mode of Astra Machina processor

- eMMC EXT\_CSD register:

- EXT\_CSD[177] for Boot partition config.

- EXT\_CSD[179] for Bus Width and Speed Mode config.

- For more information, see JESD84-B51.

#### 1.4. Internal Pull-Up resistors Control

The eMMC controller of the SL16xO SoC includes built-in internal pull-up resistors for the eMMC bus signals. The configuration and control of these resistors can be managed using the registers listed in Table 3.

Table 3. eMMC Internal Pull-Up/Dn resistor register

| Name        | Register Address | Description                                                                                                                            | Recommended<br>Value |

|-------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| CMDPAD_CNFG | 0x304[4:3]       | OxO (DISABLED): Pull-up and pull-down                                                                                                  | Ox1                  |

| DATPAD_CNFG | 0x306[4:3]       | <ul> <li>functionality disabled</li> <li>Ox1 (PULLUP): Weak pull up enabled</li> <li>Ox2 (PULLDOWN): Weak pull down enabled</li> </ul> | Ox1                  |

| CLKPAD_CNFG | 0x308[4:3]       |                                                                                                                                        | OxO                  |

| STBPAD_CNFG | Ox3OA[4:3]       | Ox3 (ILLEGAL): Should not be used                                                                                                      | Ox2                  |

Note: SL16x0: EMMC\_REG\_BASE is OxF7AA0000, SL261x: EMMC\_REG\_BASE is OxF7A00000.

## 1.5. Delay-Line Tuning

The eMMC controller of the Astra Machina SoC supports the Tuning Function for both Read and Write operations. This ensures reliable high-speed data transfers in modes such as HS200 and **HS400** by calibrating the signal timing for optimal performance.

#### 1.5.1. Read Tuning

In HS200 and HS400 modes, the host adjusts the sampling point to reliably receive data. During initialization, the host sends CMD21 (Tuning Command) to the eMMC device, which responds with a tuning pattern. The host performs the tuning sequence to find the optimal sampling point, ensuring reliable high-speed communication.

#### 1.5.2. Write Tuning

The Astra Machina processor provides an eMMC\_CLK TX Delay Line Adjustment function for all speed modes. This feature ensures optimal timing alignment for high-performance eMMC operation.

The register in Table 4 is used to configure the eMMC\_CLK TXDLY.

Table 4. eMMC CLK TXDLY register

| Name Register Address |  | Description                                   |  |  |

|-----------------------|--|-----------------------------------------------|--|--|

| SDCLKDL_DC 0x31E[6:0] |  | Drives eMMC CLK DelayLine's Delay Code input. |  |  |

Note: SL16x0: EMMC\_REG\_BASE is 0xF7AA0000, SL261x: EMMC\_REG\_BASE is 0xF7A00000.

Table 5 lists the recommended TXDLY settings for the eMMC\_CLK signal based on the speed mode.

Table 5. eMMC CLK TXDLY Recommended Setting

| Board      | eMMC Speed Mode |        |        |        |       |       |

|------------|-----------------|--------|--------|--------|-------|-------|

| Doard      | Identical       | Legacy | HS-SDR | HS-DDR | HS200 | HS400 |

| SL1680_RDK | 40              | 40     | 40     | 40     | 40    | 20    |

| SL1640_RDK | 40              | 40     | 40     | 40     | 40    | 20    |

| SL1620_RDK | 40              | 40     | 40     | 40     | 40    | 20    |

| SL261x_RDK | 40              | 40     | 40     | 40     | 40    | 20    |

## 1.6. PCB Layout Guidelines

- Minimize the length of the CLK, CMD, and DAT traces to reduce signal latency and interference.

- Use controlled impedance routing for high-speed signals (CLK, CMD), typically 50ohm Single-End.

- Match trace lengths for CLK, CMD, DATO-DAT7 to ensure proper signal timing in high-speed modes.

- Avoid crossing noisy components (e.g., switching power regulators) with high-speed signal

## 2. References

- Astra Machina™ Foundation Series Quick Start Guide (PN: 511-001404-01)

- SL1620 Embedded IoT Processor Electrical Specification Datasheet (PN: 505-001428-01)

- SL1640 Embedded IoT Processor Electrical Specification Datasheet (PN: 505-001415-01)

- SL1680 Embedded IoT Processor Electrical Specification Datasheet (PN: 505-001413-01)

- SL2610 Product Line of Embedded Processor Datasheet (PN: 505-001501-01)

- Embedded Multi-Media Card (eMMC) Electrical Standard (5.1) (JESD84-B51)

Dominos de do y Anonymous Orisonal de do y Anony

# 3. Revision History

| Revision | Description                               |

|----------|-------------------------------------------|

| А        | Initial release.                          |

| В        | Minor update to correct trademarked items |

| С        | Minor update to trademarked items.        |

| D        | Added eMMC for SL2610.                    |

#### Copyrigh

Copyright © 2025 Synaptics Incorporated. All Rights Reserved.

#### Trademarks

Astra Machina, SyNAP, Synaptics and the Synaptics logo are trademarks or registered trademarks of Synaptics Incorporated in the United States and/or other countries.

Android is a trademark of Google LLC, Linux is the registered trademark of Linus Torvalds in the U.S. and other countries. All other trademarks are the properties of their respective owners.

#### Contact Us

Visit our website at www.synaptics.com to locate the Synaptics office nearest you.

PN: 506-001594-01 Rev D

#### Notic

Use of the materials may require a license of intellectual property from a third party or from Synaptics. This document conveys no express or implied licenses to any intellectual property rights belonging to Synaptics or any other party. Synaptics may, from time to time and at its sole option, update the information contained in this document without notice.

INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED "AS-IS," AND SYNAPTICS HEREBY DISCLAIMS ALL EXPRESS OR IMPLIED WARRANTIES, INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, AND ANY WARRANTIES OF NON-INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT SHALL SYNAPTICS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES ARISING OUT OF OR IN CONNECTION WITH THE USE OF THE INFORMATION CONTAINED IN THIS DOCUMENT, HOWEVER CAUSED AND BASED ON ANY THEORY OF LIABILITY, WHETHER IN AN ACTION OF CONTRACT, NEGLIGENCE OR OTHER TORTIOUS ACTION, AND EVEN IF SYNAPTICS WAS ADVISED OF THE POSSIBILITY OF SUCH DAMAGE. IF A TRIBUNAL OF COMPETENT JURISDICTION DOES NOT PERMIT THE DISCLAIMER OF DIRECT DAMAGES OR ANY OTHER DAMAGES, SYNAPTICS' TOTAL CUMULATIVE LIABILITY TO ANY PARTY SHALL NOT EXCEED ONE HUNDRED US. DOLLARS.