# Astra™ SL1620 Embedded IoT Processor Functional Specification

PN: 505-001456-01 Rev.C

Donald State of the State of th

# Contents

|     | Ü            |                                                                                                          |

|-----|--------------|----------------------------------------------------------------------------------------------------------|

| 1.  | Archite      | cture Overview                                                                                           |

|     | 1.1.         | Key Components and Sub-systems                                                                           |

|     |              | 1.1.1. Global Unit                                                                                       |

|     |              | 1.1.2. CPU (Arm Cortex A55 DSU Sub-system)                                                               |

|     |              | 1.1.3. Boot ROM                                                                                          |

|     |              | 1.1.4. Security Island Sub-system (SISS)                                                                 |

|     |              | 1.1.5. DDR Memory Controller                                                                             |

|     |              | 1.1.6. Graphics Engine                                                                                   |

|     |              | 1.1.7. Video Post Processing (VPP)                                                                       |

|     |              | 1.1.8. Audio Input/Output (AIO)                                                                          |

|     |              | 1.1.9. SoC Connectivity and Access Control                                                               |

|     |              | 1.1.10. Peripheral Sub-system                                                                            |

|     |              | 1.1.8. Audio Input/Output (AIO) 1.1.9. SoC Connectivity and Access Control 1.1.10. Peripheral Sub-system |

| 2.  | Global       | Jnit                                                                                                     |

|     | 2.1.         | Overview                                                                                                 |

|     | 2.2.         | Functional Description1                                                                                  |

|     |              | 2.2.1. Reset Module                                                                                      |

|     |              | 2.2.2. Reset Sources                                                                                     |

|     |              | 2.2.3. Software Reset Scheme                                                                             |

|     |              | 2.2.4. External Reset Sequence                                                                           |

|     |              | 2.2.5. Clock Module                                                                                      |

|     |              | 2.2.6. PLL and Oscillator                                                                                |

|     |              | 2.2.7. Clock Dividers and Switches                                                                       |

|     |              | 2.2.8. Clock Switching Procedure                                                                         |

|     |              | 2.2.9. Boot Strap Module                                                                                 |

| 3.  | CPU          |                                                                                                          |

|     | 3.1.         | CortexA55 DSU Sub-system1                                                                                |

|     | 3.2.<br>3.3. | Reference Documents A                                                                                    |

|     |              | Module Revision                                                                                          |

|     | 3.4.         | CPU Clock                                                                                                |

| 4.  | Poot D       | ıM 2                                                                                                     |

| 4.  | 4.1.         | Overview                                                                                                 |

|     | 4.1.         | SL1620 ROM Code Flow                                                                                     |

|     | 4.2.         | Flash Layout                                                                                             |

|     | 4.3.         | 4.3.1. Multi-copies, Magic Number, and ECC Attributes in Page 0, Block 0                                 |

|     |              | 4.3.2. SPI Flash for SPI-Secure Boot                                                                     |

|     |              | 4.3.3. eMMC Layout                                                                                       |

|     |              | 4.3.4. Boot Operation Mode in eMMC                                                                       |

|     |              | 4.3.5. eMMC Boot in SL1620 Device                                                                        |

|     |              | 4.3.6. eMMC Boot Mode                                                                                    |

|     |              |                                                                                                          |

| 5.  |              |                                                                                                          |

|     | 5.1.         | Overview                                                                                                 |

|     | 5.2.         | JTAG Debug Port Configurations2                                                                          |

|     | 5.3.         | Boundary Scan Support2                                                                                   |

| 6.  | SoC Co       | nnectivity and Access Control2                                                                           |

| 2.5 | 6.1.         | Connection Table                                                                                         |

|     |              | 6.1.1. Address Map                                                                                       |

| 7.  | Securi<br>7.1. | ty Island Subsystem                                             |    |

|-----|----------------|-----------------------------------------------------------------|----|

|     | 7.1.<br>7.2.   | OTP                                                             |    |

| 8.  |                | 1emory Controller                                               |    |

|     | 8.1.           | Introduction                                                    |    |

|     | 8.2.           | Memory Controller Feature List                                  |    |

|     | 8.3.           | DDR Memory Controller Overview                                  |    |

|     | 8.4.<br>8.5.   | Functional Description                                          |    |

| 0   |                |                                                                 |    |

| 9.  | Grapn<br>9.1.  | ics Engine                                                      |    |

|     | 9.1.           | 9.1.1. GPU Key Features                                         |    |

|     |                | 9.1.2. Unified Shading Cluster Features                         |    |

|     |                | 9.1.3. 3D Graphics Features                                     |    |

|     |                | 9.1.4. Compute Features                                         | 38 |

|     |                | 9.1.5. TFBC Features                                            |    |

|     | 9.2.           | GPU Integration Overview                                        | 39 |

|     | 9.3.           | GPU Bus Interface                                               | 4  |

|     |                | 9.3.1. AXI Host Interface                                       | 4  |

|     |                | 9.3.2. AXI SoC Interface                                        |    |

|     | 9.4.           | Performance Characteristics                                     |    |

| 10  | 9.5.           | GPU Architecture Overview  Post Processing (VPP)  Overview      | 44 |

| 10. | Video          | Post Processing (VPP)                                           | 45 |

|     | 10.1.<br>10.2. | Overview                                                        |    |

|     | 10.2.          | LCDC Controller Configuration                                   |    |

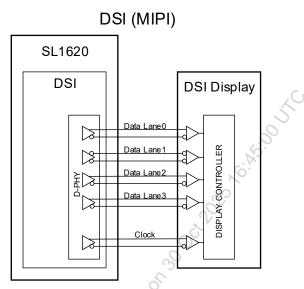

|     | 10.0.          | 10.3.1. LCD with Display Serial Interface (MIPI)                |    |

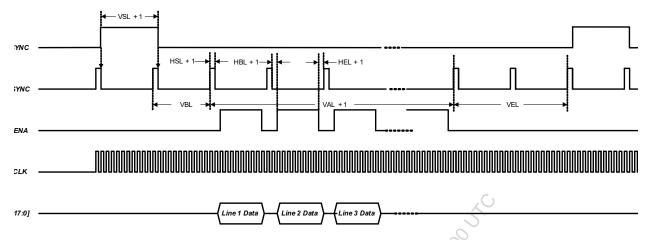

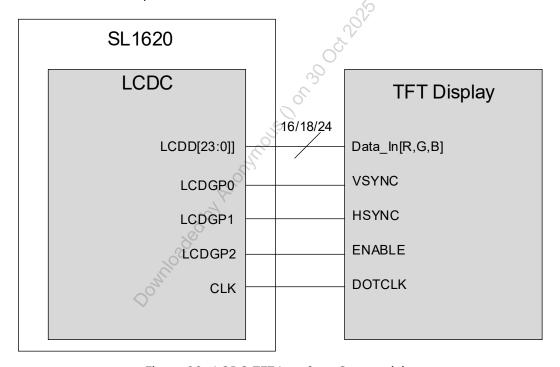

|     |                | 10.3.2. TFT Interface                                           |    |

|     |                | 10.3.3. STN Interface                                           |    |

|     |                | 10.3.4. LCDC Output Pin                                         |    |

|     |                | 10.3.5. CPU-Type Interface                                      |    |

|     |                | 10.3.6. General-Purpose Output for Row/Column Driver            |    |

|     |                | 10.3.7. LCDC interface handshake signal Pin-out Mapping Summary |    |

| 11. |                | Input Output                                                    |    |

|     | 11.1.          | Overview                                                        |    |

|     | 11.2.          | Addit Clock Collottic                                           |    |

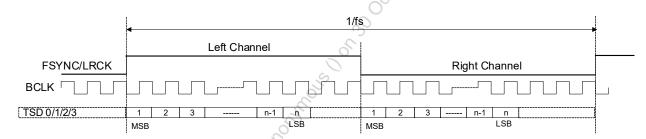

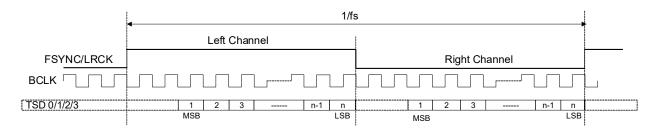

|     | 11 0           | 11.2.1. Sampling Rate and Bit Clock                             |    |

|     | 11.3.          | Data Formats                                                    |    |

|     |                | 11.3.2. Left-Justified Mode                                     |    |

|     |                | 11.3.3. Right-Justified Mode                                    |    |

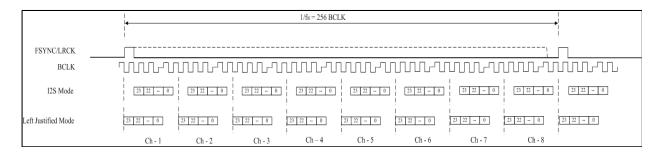

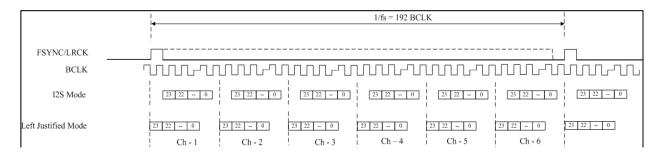

|     |                | 11.3.4. Time Division Multiplexed (TDM) Mode                    |    |

|     | 11.4.          | PCM Mono Mode                                                   |    |

|     | 11.5.          | Pulse Density Modulation (PDM) Mode                             | 63 |

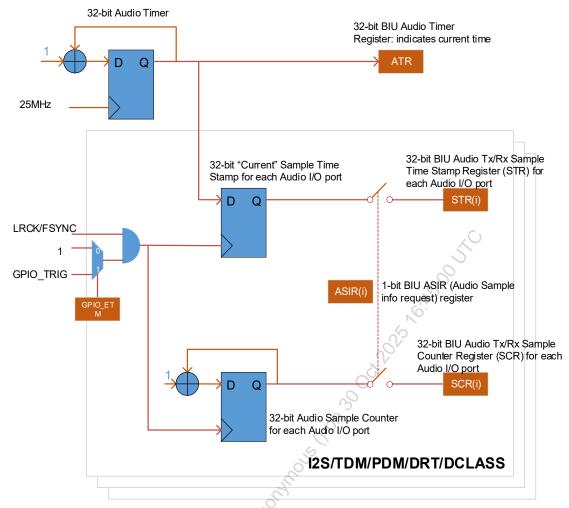

|     | 11.6.          | Audio Sample Counter & Timestamp                                |    |

|     | 11.7.          | Audio Accurate Playback/Recording Trigger (AAPRT)               |    |

|     | 11.8.          | Audio Playback/Recording Pause/Restart                          |    |

|     | 11.9.          | I2S/TDM HW/SW Mute                                              |    |

|     | 11.10.         | PTRACK                                                          |    |

| 12. | •              | eral Subsystem                                                  |    |

|     | 12.1.          | Introduction                                                    |    |

|     | 12.2.          | Description                                                     | 66 |

| 13. | NAND   | Flash Controller                                                     | 67             |  |  |

|-----|--------|----------------------------------------------------------------------|----------------|--|--|

|     | 13.1.  | Features                                                             | 67             |  |  |

|     | 13.2.  | NAND Timing Registers                                                |                |  |  |

| 14. | APB C  | Components of Peripheral Interface                                   | 68             |  |  |

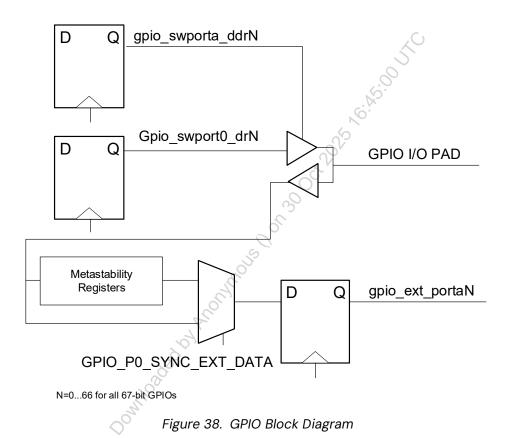

|     | 14.1.  | General Purpose Input/Output (GPIO)                                  |                |  |  |

|     |        | 14.1.1. GPIO as I/O Pins                                             |                |  |  |

|     | 14.2.  | Two-Wire Serial Interface (TWSI)                                     |                |  |  |

|     |        | 14.2.1. Overview                                                     |                |  |  |

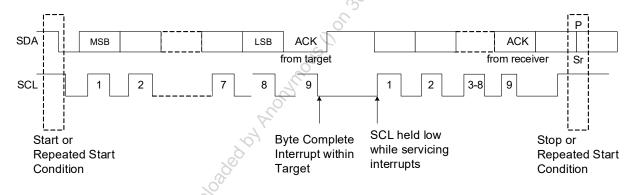

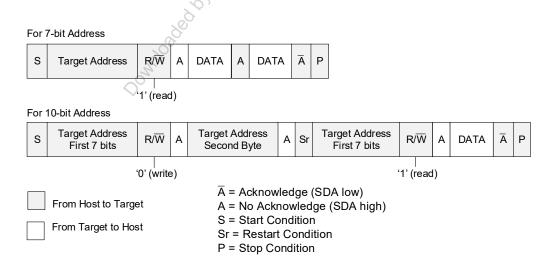

|     |        | 14.2.2. TWSI Protocols                                               |                |  |  |

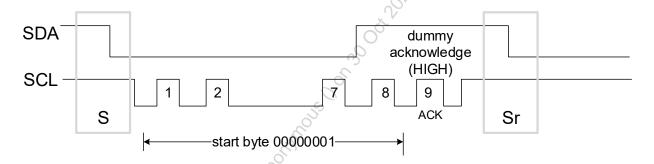

|     |        | 14.2.3. START BYTE Transfer Protocol                                 |                |  |  |

|     |        | 14.2.4. Multiple Host Arbitration and Clock Synchronization          |                |  |  |

|     |        | 14.2.5. Operation Model                                              |                |  |  |

|     | 14.3.  | Timers                                                               |                |  |  |

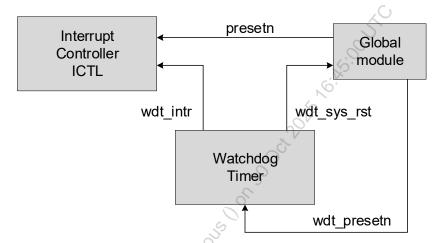

|     | 14.4.  | Watchdog Timers (WDT)                                                | 78             |  |  |

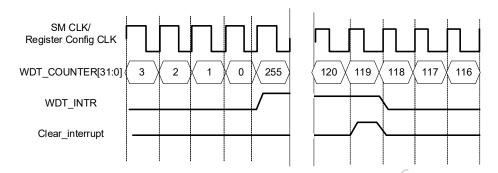

|     |        | 14.4.1. Counter                                                      | 78             |  |  |

|     |        | 14.4.2. Interrupts                                                   | 78             |  |  |

|     |        | 14.4.2. Interrupts 14.4.3. System Resets Serial Peripheral Interface | 79             |  |  |

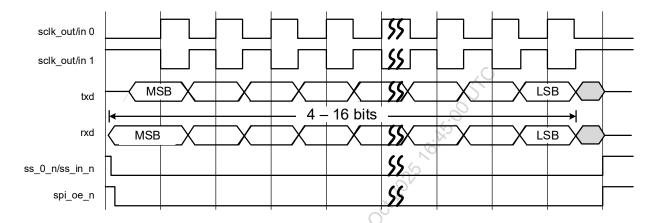

|     | 14.5.  | Serial Peripheral Interface                                          | 79             |  |  |

|     |        | 14.5.1. Overview                                                     | 80             |  |  |

|     |        | 14.5.2. Clock Ratios                                                 |                |  |  |

|     |        | 14.5.3. Transmit and Receive FIFO Buffers                            | 8              |  |  |

|     |        | 14.5.4. SPI Interrupts                                               | 82             |  |  |

|     |        | 14.5.4. SPI Interrupts                                               | 82             |  |  |

|     |        | 14.5.6. Operation Modes                                              | 83             |  |  |

|     |        | 14.5.7. Data Transfers                                               | 84             |  |  |

|     |        | 14.5.8. Serial Peripheral Interface (SPI) Protocol                   |                |  |  |

| 15  | 0D 11- |                                                                      |                |  |  |

| 15. | 2D H0  | ost                                                                  | 86             |  |  |

|     | 15.1.  | SDIO HOST Controller Features                                        | 80             |  |  |

|     | 15.2.  | SDIO PHY Features                                                    |                |  |  |

| 16. | eMMC   | C Host                                                               | 88             |  |  |

|     | 16.1.  | eMMC Host Controller Features                                        |                |  |  |

|     | 16.2.  | eMMC PHY Features                                                    | 89             |  |  |

|     | 16.3.  | DigiLogic-Specific Features                                          |                |  |  |

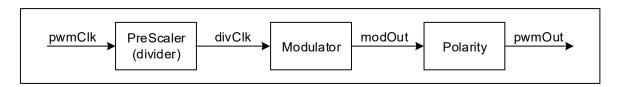

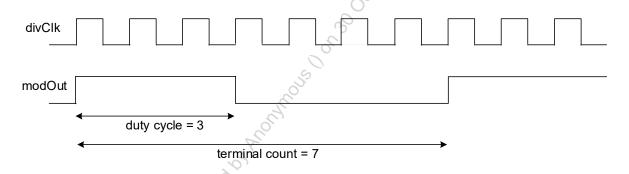

| 17. | Dulco  | Width Modulator (PWM)                                                | 00             |  |  |

| 17. | 17.1.  | Overview                                                             |                |  |  |

|     | 17.1.  | Overview                                                             |                |  |  |

| 18. | USB 2  | .0 Host                                                              |                |  |  |

|     | 18.1.  | USB Controller Features                                              | 9 <sup>.</sup> |  |  |

|     | 18.2.  | USB PHY Features                                                     | 92             |  |  |

| 19. | HCD 2  | .0 Host                                                              | 03             |  |  |

| 19. | 19.1.  | Overview                                                             |                |  |  |

|     | 19.1.  | 19.1.1. Features                                                     |                |  |  |

|     |        |                                                                      |                |  |  |

| 20. | 10/100 | D/1000 Mbps (Gigabit) Ethernet Controller                            |                |  |  |

|     | 20.1.  | Functional Overview                                                  |                |  |  |

|     | 20.2.  | Features                                                             | 94             |  |  |

| 21. | Refere | ences                                                                | 96             |  |  |

|     |        |                                                                      |                |  |  |

| 22. | Revisi | Revision History                                                     |                |  |  |

# List of Tables

| Table 1.  | PLLs and Output Frequency                               | 14 |

|-----------|---------------------------------------------------------|----|

| Table 2.  | SL1620 Clocks                                           |    |

| Table 3.  | Cortex-A55 DSU Configuration Options                    | 20 |

| Table 4.  | ARM IP Revision                                         | 21 |

| Table 5.  | SoC Boot Source                                         | 23 |

| Table 6.  | SL1620 Debug Port Configuration                         | 28 |

| Table 7.  | SL1620 Supported Instructions                           | 28 |

| Table 8.  | Host and Target Pair Connection Levels                  | 30 |

| Table 9.  | System Memory Map                                       | 30 |

| Table 10. | Low-Speed Register Memory Map                           | 31 |

| Table 11. | Features of GPU AXI Host Interface                      |    |

| Table 12. | Features of GPU AXI SoC Interface                       | 42 |

| Table 13. | GPU Core Performance Characteristics                    |    |

| Table 14. | LD Values for TFT LCD Panel                             |    |

| Table 15. | TFT LD[23:0] Connectivity                               | 50 |

| Table 16. | LCDC Output Pins                                        | 51 |

| Table 17. | TFT LD[23:0] Connectivity (CPU display)                 | 54 |

| Table 18. | Interface Pinout                                        | 55 |

| Table 19. | Audio Output paths/ports                                | 56 |

| Table 20. | Audio Input paths/ports                                 | 57 |

| Table 21. | Sampling Rate and Bit Clock Relationship (I2S)          | 59 |

| Table 22. | Sampling Rate and Bit Clock Relationship (For TDM Mode) | 59 |

| Table 23. | PTRACK sources                                          | 65 |

| Table 24. | TWSI Definition of Bits in the First Byte               | 73 |

# List of Figures

| Figure 1.  | SL1620 architecture block diagram                   | 8              |

|------------|-----------------------------------------------------|----------------|

| Figure 2.  | SL1620 Global Unit Block                            | 11             |

| Figure 3.  | SL1620 Power-up Sequence                            |                |

| Figure 4.  | SL1620 Clock Generation Structure                   |                |

| Figure 5.  | Cortex-A55 DSU Block Diagram                        | 19             |

| Figure 6.  | ROM Code Flow                                       | 23             |

| Figure 7.  | SPI Flash Layout for SPI-Secure Boot                | 24             |

| Figure 8.  | State Diagram of Boot Mode                          | 25             |

| Figure 9.  | State Diagram of Alternative Boot Mode              | 25             |

| Figure 10. | Layout of eMMC Device                               |                |

| Figure 11. | JTAG Chain and Boundary Scan diagram                | 27             |

| Figure 12. | SL1620 Bus Hosts and Targets                        | 29             |

| Figure 13. | DDR Memory Controller Top-Level Block Diagram       | 34             |

| Figure 14. | DDRPHY Block Diagram                                |                |

| Figure 15. | BXE-2-32 core in SoC                                | 39             |

| Figure 16. | GPU High-Level Architecture                         | 44             |

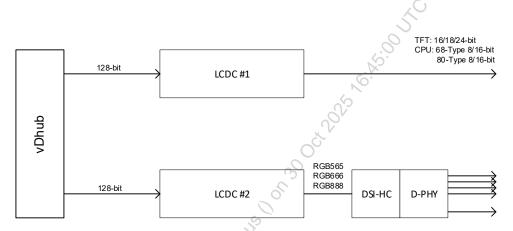

| Figure 17. | SL1620 Video Processing Pipe                        | 45             |

| Figure 18. | SL1620 DSI Connectivity                             | 47             |

| Figure 19. | TELLOD panel unling                                 | <del>4</del> 9 |

| Figure 20. |                                                     | 49             |

| Figure 21. | LD Timing for STN LCD Panel                         |                |

| Figure 22. | STN LCD Panel Timing                                |                |

| Figure 23. | Output MUX for Control Signal                       | 53             |

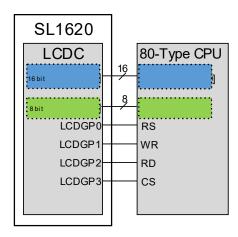

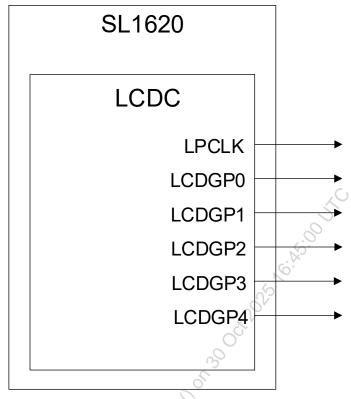

| Figure 24. | 68-Type CPU Interface, One 16-Bit and One 8-Bit Bus |                |

| Figure 25. | 80-Type CPU Interface, One 16-Bit and One 8-Bit Bus |                |

| Figure 26. | 80-Type CPU Interface, One 16-Bit and One 8-Bit Bus |                |

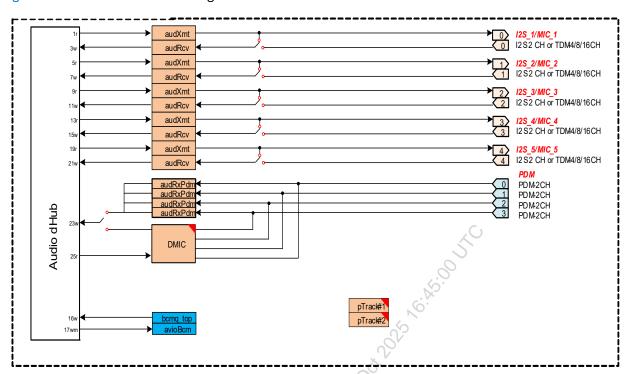

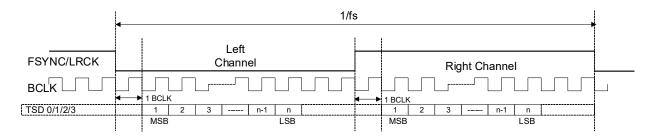

| Figure 27. | Functional Block Diagram of AIO Module              |                |

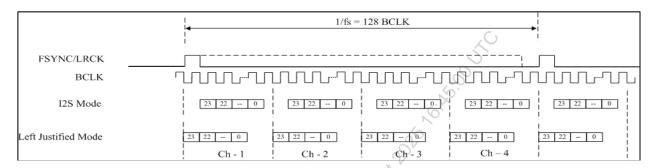

| Figure 28. | l <sup>2</sup> S Mode                               |                |

| Figure 29. | Left-Justified Mode                                 | 60             |

| Figure 30. |                                                     |                |

| Figure 31. | 8-Channel TDM Mode Data                             |                |

| Figure 32. | 6-Channel TDM Mode Data                             | 62             |

| Figure 33. | 4-Channel TDM Mode Data                             | 62             |

| Figure 34. | 2-Channel TDM Mode Data                             | 62             |

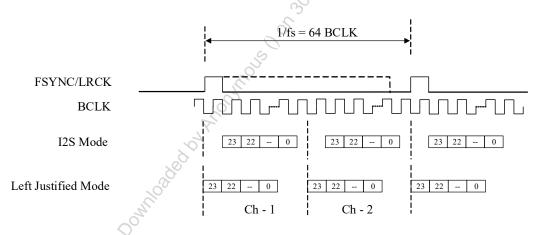

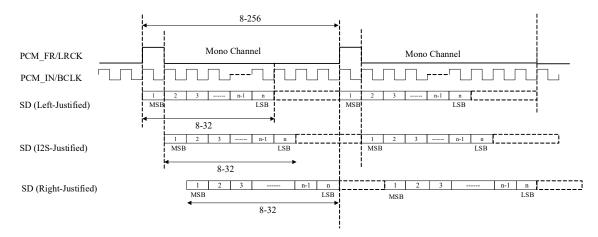

| Figure 35. | PCM Mono Mode Data                                  | 63             |

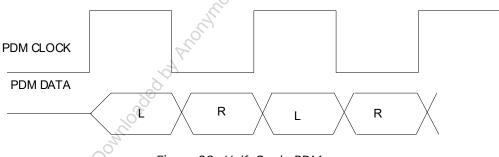

| Figure 36. | Half-Cycle PDM                                      | 63             |

| Figure 37. | Audio Sample Counter & Timestamp                    | 64             |

| Figure 38. | GPIO Block Diagram                                  | 68             |

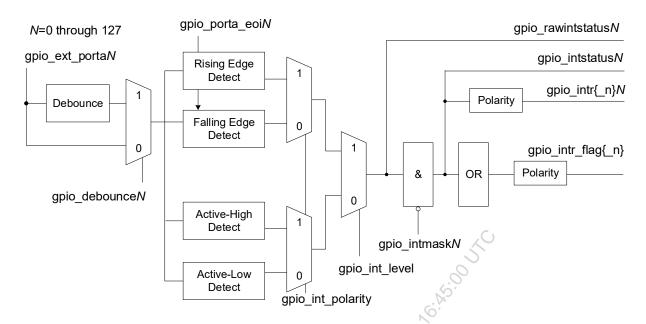

| Figure 39. | GPIO Interrupt Block Diagram                        | 70             |

| Figure 40. | TWSI Start and Stop Condition                       |                |

| Figure 41. | START and STOP Condition                            | 72             |

| Figure 42. | 7-Bit Address Format                                |                |

| Figure 43. |                                                     |                |

| Figure 44. | Host-Transmitter Protocol                           | 74             |

| Figure 45. | Host-Receive Protocol                               | 74             |

| Figure 46. | Start Byte Transfer                | 75 |

|------------|------------------------------------|----|

| Figure 47. | Example Watchdog Timer             | 78 |

| Figure 48. | Interrupt Generation               | 79 |

| Figure 49. | Counter Restart and System Restart | 79 |

| Figure 50. | Hardware Target Selection          | 80 |

| Figure 51. | Maximum SCLK_OUT/SPI_CLK Ratio     | 8  |

| Figure 52. | SPI Host Device                    | 84 |

| Figure 53. | SPI Serial Format (SCPH = 0)       | 85 |

| Figure 54. | PWM Block Diagram                  | 90 |

| Figure 55. | Waveform                           | 90 |

Downloaded by Anonymous Oor 2012 (c.) Asia Discourse (c.) Asia Discours

#### 1. Architecture Overview

This document provides an in-depth description of the architecture, sub-systems, and operational characteristics of the Synaptics Astra™ SL1620 embedded IoT processor. This document is essential for developers and engineers who are integrating the SL1620 into their systems, offering comprehensive details on each sub-system and their interactions.

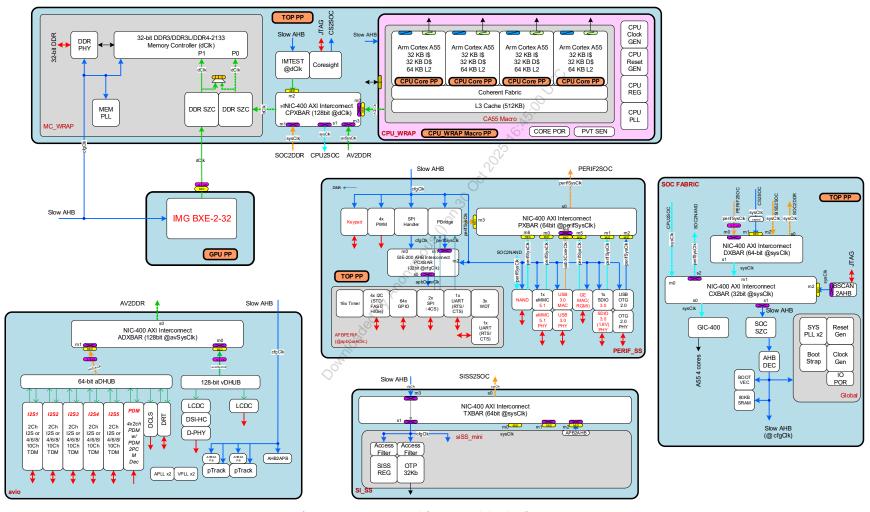

Figure 1. SL1620 architecture block diagram

#### 1.1. Key Components and Sub-systems

#### 1.1.1. Global Unit

The Global Unit manages the core functionalities of the SL1620, including clock generation, reset signals, and bootstrapping. It encompasses modules such as the Clock Module, Reset Module, and Boot Strap Module, which work together to ensure the processor operates correctly from power-up through normal operation. The Clock Module includes multiple PLLs that generate the necessary frequencies for the device's various subsystems.

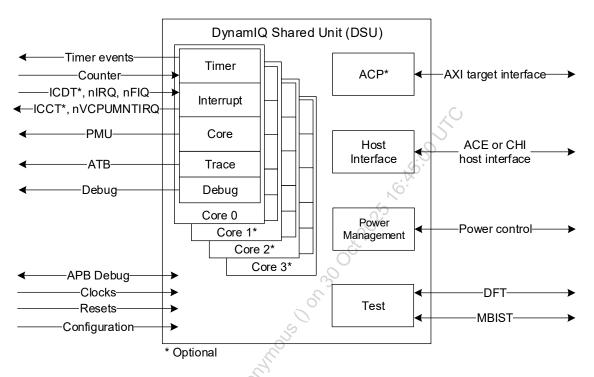

#### 1.1.2. CPU (Arm Cortex A55 DSU Sub-system)

The SL1620 is powered by a quad-core Arm® Cortex® A55 processor, integrated within a DynamlQ Shared Unit (DSU). This subsystem is responsible for the main processing tasks and includes L3 cache for enhanced performance. The CPU subsystem supports a variety of interfaces for debugging and system management.

#### 1.1.3. Boot ROM

The Boot ROM handles the initial boot process of the SL1620, including secure boot options. It supports multiple boot scenarios, such as SPI-Secure, eMMC-Secure, and USB-Secure boot modes, ensuring a flexible and secure startup process.

#### 1.1.4. Security Island Sub-system (SISS)

The SISS is critical for managing security features within the SL1620. It includes OTP (One-Time Programmable) memory, supporting secure key management, encryption/decryption, and other cryptographic operations.

#### 1.1.5. DDR Memory Controller

The DDR Memory Controller interfaces with the system's DDR memory, handling the queuing and scheduling of memory transactions. It supports dynamic scheduling, multiple traffic classes for quality of service (QoS), and features like write-combining and out-of-order execution to optimize performance.

#### 1.1.6. Graphics Engine

The SL1620 includes a high-performance graphics engine based on the Imagination B-Series BXE-2-32 core. This GPU supports advanced 3D graphics features, such as tile-based deferred rendering, programmable shading, and high SIMD efficiency. It is compliant with multiple graphics APIs, including OpenGL, Vulkan, and OpenCL, making it suitable for rich graphical applications.

#### 1.1.7. Video Post Processing (VPP)

The VPP module handles video processing tasks, including interfacing with LCD panels or MIPI panels. It supports various display interfaces and formats, such as RGB and CPU-type interfaces, and includes features for brightness control, gamma correction, and partial refresh for power-saving modes.

#### 1.1.8. Audio Input/Output (AIO)

The AIO module manages the transmission and reception of audio streams, supporting formats like I2S, TDM, and PCM. It handles both audio input and output, ensuring high-quality audio processing for applications like media playback and recording.

#### 1.1.9. SoC Connectivity and Access Control

This subsystem links the CPU and hardware engines with various targets, including DRAM and external flash memory. It manages data routing and access control, ensuring secure and efficient communication between different parts of the system.

#### 1.1.10. Peripheral Sub-system

The peripheral sub-system includes interfaces for general-purpose input/output (GPIO), serial communication, timers, and watchdog timers. These components allow the SL1620 to interact with external devices and sensors, extending its functionality in embedded applications.

#### 1.1.11. JTAG and Debugging Interfaces

The JTAG interface supports debugging through In-Circuit Emulation (ICE) and boundary scan, crucial for hardware validation and troubleshooting. It includes security features to protect against unauthorized access during debugging.

#### 2. Global Unit

#### 2.1. Overview

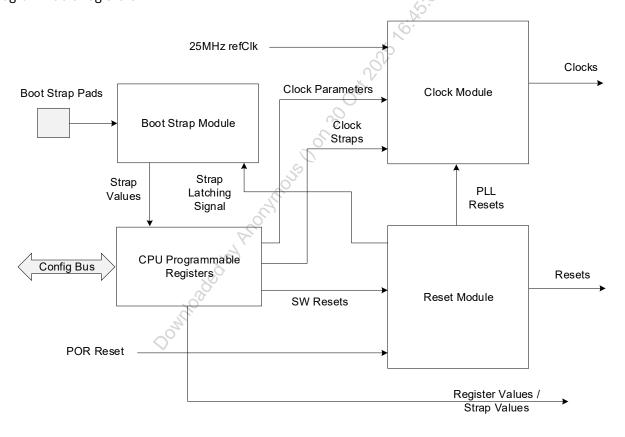

The SL1620 device relies on the Global Unit to provide on-chip clocking and reset signals. The Global Unit also handles all the chip and system-level control. The Global Unit includes a clock module, reset module, boot strap module, and CPU Programmable Registers. Figure 2 depicts the relationships among these modules.

The Reset Module takes the system reset signal from POR pad and resets from CPU- controlled registers to create individual resets to each subsystem. The Boot Strap Module latches the strapping values from the pads 320 ns (8 cycles of 25 MHz clock) after SoC reset, or POR changes from low to high. The strap values are kept in registers for the CPU to read and the same registers are also used directly to configure the SL1620 device. In this way, the boot strap register values and the actual configuration are always consistent. The boot straps are used to select SL1620 clock generation and CPU boot options. The strap description is found in the *SL1620 Datasheet* (PN: 505-001428-01). The Clock Module includes 8 PLLs that generate required frequencies, and clock divider/switching logic for all the subsystems of the SL1620 device. The clock parameters are controlled by CPU programmable registers.

Figure 2. SL1620 Global Unit Block

#### 2.2. Functional Description

#### 2.2.1. Reset Module

Separate reset signals are generated for each clock domain on which a particular sub-system operates.

#### 2.2.2. Reset Sources

There are five sources to trigger each individual reset:

- Reset from RSTIn pad

- Reset from POR\_VDD (monitor Core VDD)

- Reset from POR\_IO\_VDD (monitor IO power supply)

- Watchdog reset

- · Register controlled module reset

#### 2.2.3. Software Reset Scheme

The SL1620 device uses a pair of reset registers (reset trigger register and reset status register) to facilitate the software reset. When software writes 1 to a reset trigger register bit, it results in the assertion of the corresponding reset for 16 reference clock cycles (25 MHz). The corresponding reset status bit is set to 1 until cleared by software. The CPU can access both the reset trigger register and reset status register.

#### 2.2.4. External Reset Sequence

During the hardware reset, the SL1620 device prevents the CPU from booting up earlier than the remainder of the SoC by de-asserting the CPU reset after all other resets are de-asserted.

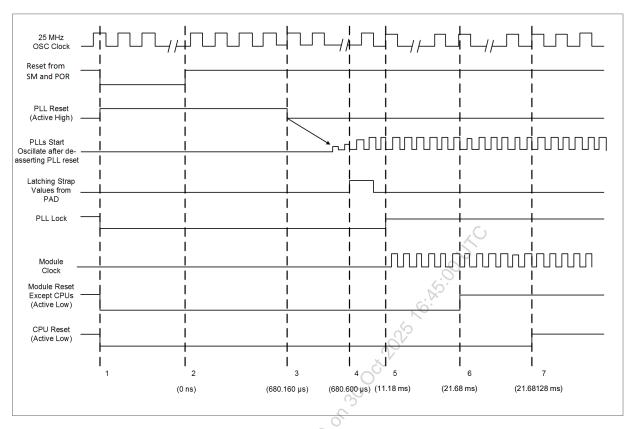

The power-up reset sequence is as follows:

- 1. External Reset pin is asserted, hardware reset occurs. The full SL1620 device is reset immediately.

- 2. External Reset is de-asserted. The SL1620 device reset state machine initiates.

- 3. SL1620 internal reset state machine de-asserts PLL reset. PLL starts to oscillate and lock.

- 4. SL1620 device latches power-on setting from strap pins.

- 5. PLLs are locked and stable clocks are driven to the modules after 1 ms.

- 6. Global reset is de-asserted to all modules (except CA55 CPU) after 1ms.

- 7. De-assert CPU resets after 32 cycles (25 MHz)

Figure 3 shows the SL1620 power-up sequence.

Figure 3. SL1620 Power-up Sequence

#### 2.2.5. Clock Module

The clock module generates the clocks to each sub-system in the SL1620 device using PLLs and dividers.

#### 2.2.6. PLL and Oscillator

The clock module has an internal oscillator to generate a stable reference clock to the PLLs using external 25 MHz crystal.

Table 1 lists the PLLs which are present in the clock modules and their corresponding frequency outputs.

Table 1. PLLs and Output Frequency

| # | PLL        | Frequency<br>Output Range | Output Frequency<br>formula                      | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---|------------|---------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | Memory PLL | 20 MHz - 3 GHz            | CLKOUT<br>=(DIVFI[8:0])*4 / DIVR *<br>25 / DIVQ  | Users can change the Feedback divider FBDIV values and VCO divider VCODIV value to obtain the preferred PLL frequency.  The following block clocks are provided by this PLL during reset default:  DDR Memory Controller  DDR PHY                                                                                                                                                                                                                                       |

| 2 | CPU PLL    | 20 MHz - 3 GHz            | CLKOUT =<br>(DIVFI[8:0])*4 / DIVR *<br>25 / DIVQ | User can change the Feedback divider FBDIV values and VCO divider VCODIV value to obtain the preferred PLL frequency.  CPU clock is provided by this PLL during reset default.                                                                                                                                                                                                                                                                                          |

| 3 | System PLL | 20 MHz - 3 GHz            | CLKOUT =<br>(DIVFI[8:0])*4 / DIVR *<br>25 / DIVQ | Users can change the Feedback divider FBDIV values and VCO divider VCODIV value to obtain the preferred PLL frequency.  The following block clocks are provided by this PLL during reset default:  Peripheral sub-system  Audio post-processor  Video post-processor  The following block clocks are provided by this PLL during reset default:  Peripheral sub-system  Audio post-processor  The following block clocks are provided by this PLL during reset default: |

| 4 | APLLO/1    | 20 MHz - 3 GHz            | CLKOUT<br>=(DIVFI[8:0])*4 / DIVR *<br>25 / DIVQ  | There are 2 independent APLL PLLs (APLLO and APLL1). User can change Feedback divider DIVFI, DIVR and DIVQ values to obtain the preferred PLL frequency for APLLO and APLL1 respectively. The final clock output is also determined by its corresponding interpreter frequency offset and PPM offset setting.  Audio are provided by these PLLs during reset default.                                                                                                   |

| 5 | VPLLO/1    | 20 MHz - 3 GHz            | CLKOUT =<br>(DIVFI[8:0])*4 / DIVR *<br>25 / DIVQ | There are 2 independent VPLL PLLs (VPLLO and VPLL1). User can change Feedback divider DIVFI, DIVR and DIVQ values to obtain the preferred PLL frequency for VPLLO and VPL1 respectively. The final clock output is also determined by its corresponding interpreter frequency offset and PPM offset setting. Video pixel clocks are provided by these PLLs during reset default.                                                                                        |

PLL frequencies can be adjusted without affecting the normal SoC operation with the following programming sequence:

- Switch clock source to reference clock by setting the clock into bypass mode.

Note: Using PLL-generated clock registers to change PLL parameters is prohibited.

- Set the PLL Bypass register bit.

- Assert the PLL Reset.

- Program PLL to the new preferred frequency by changing its corresponding parameters.

- De-assert the PLL Reset after 2µs and have PLL re-LOCK with the new setting.

- Wait for the PLL to lock (max 10 μs).

- Remove PLL Bypass.

- Switch clock source back to PLL clock output.

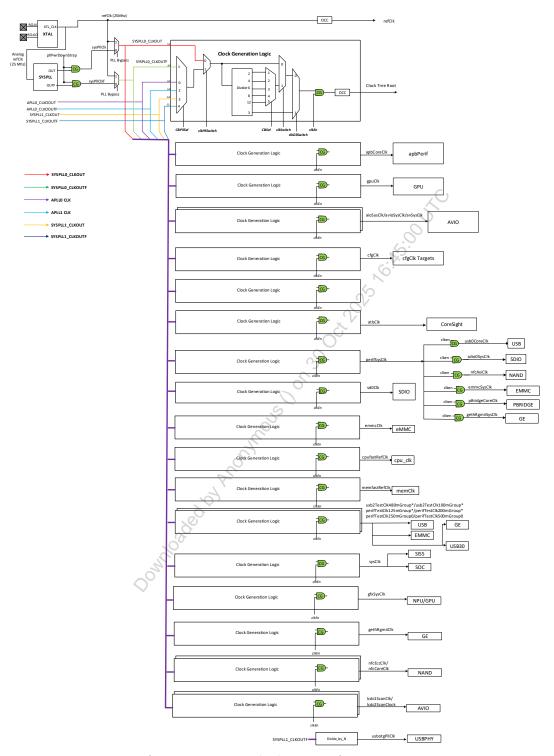

#### 2.2.7. Clock Dividers and Switches

The SL1620 device clock divider creates divide-by-1, divide-by-2, divide-by-3, divide-by-4, divide-by-6, divide-by-8, and divide-by-12 clocks for each individual module. To provide more flexibility of clock sources, the SL1620 device also allows most of the clocks selected from AVPLL\_B[7:4] outputs as their clock divider source clock. Table 2 lists the main clocks in SL1620 device and corresponding options available to select the clock sources.

Table 2. SL1620 Clocks

| #  | Clock                           | Clock Source Options                 | Clock Divider Options    | Max<br>Frequency |

|----|---------------------------------|--------------------------------------|--------------------------|------------------|

| 1  | DDRPHY Clock                    | Memory PLL                           | None                     | 2133             |

| 2  | Memory Controller Clock         | Memory PLL                           | Divide by 4              | 533              |

| 3  | CPU Clock                       | CPU PLL                              | Divide by 1/2/3/4/6/8/12 | 1600             |

| 4  | AXI System Clock                | System PLLO/1 or 2 outputs from APLL | Divide by 1/2/3/4/6/8/12 | 300              |

| 5  | Register Configuration<br>Clock | System PLLO/1 or 2 outputs from APLL | Divide by 1/2/3/4/6/8/12 | 100              |

| 6  | APB Peripheral Core<br>Clock    | System PLLO/1 or 2 outputs from APLL | Divide by 1/2/3/4/6/8/12 | 200              |

| 7  | AVIO AXI Clock                  | System PLLO/1 or 2 outputs from APLL | Divide by 1/2/3/4/6/8/12 | 100              |

| 8  | GPU Core Clock                  | System PLLO/1 or 2 outputs from APLL | Divide by 1/2/3/4/6/8/12 | 800              |

| 9  | GPU AXI Clock                   | Same as Memory Controller Clock      | None                     | 533              |

| 10 | eMMC Core Clock                 | System PLLO/1 or 2 outputs from APLL | Divide by 1/2/3/4/6/8/12 | 200              |

| 11 | SD Core Clock                   | System PLLO/1 or 2 outputs from APLL | Divide by 1/2/3/4/6/8/12 | 200              |

| 12 | NAND Flash Core Clock           | System PLLO/1 or 2 outputs from APLL | Divide by 1/2/3/4/6/8/12 | 200              |

| 13 | NAND Flash BCH Clock            | System PLLO/1 or 2 outputs from APLL | Divide by 1/2/3/4/6/8/12 | 200              |

| 14 | USB Core Clock                  | System PLLO/1 or 2 outputs from APLL | Divide by 1/2/3/4/6/8/12 | 200              |

Table 2. SL1620 Clocks (Continued)

| #  | <i>‡</i> | Clock           | Clock Source Options                 | Clock Divider Options    | Max<br>Frequency |

|----|----------|-----------------|--------------------------------------|--------------------------|------------------|

| 15 | 5        | USB3 Core Clock | System PLLO/1 or 2 outputs from APLL | Divide by 1/2/3/4/6/8/12 | 400              |

| 16 | 6        | GMAC Core Clock | System PLLO/1 or 2 outputs from APLL | Divide by 1/2/3/4/6/8/12 | 250              |

The SL1620 device's individual clock divider and clock multiplexer settings could be changed dynamically during the operation. For the clock generation structure, see Figure 4.

Figure 4. SL1620 Clock Generation Structure

#### 2.2.8. Clock Switching Procedure

The clock generation scheme provides dynamic clock switching capability. Here is the programming pseudo code to illustrate the dynamic clock frequency change sequence using clock switching circuit shown in Figure 4.

#### 2.2.9. Boot Strap Module

The SL1620 device boot strap pins are shared with chip output pins. The SL1620 device is the only driver of those pins in the system. During boot-up, the SL1620 device sets those pins to input mode and external pull-up/pull-down resistors pull the boot strap pins to required levels. After boot strap latching window, those pins can be driven by the SoC to any level without affecting the bootstraps. The strapping information, which can be read by the CPU, is used to configure the SL1620 device. For detailed definitions of boot strap pin assignments and functions, see the *SL1620 Datasheet* (PN: 505–001375–01).

#### 3. CPU

The SL1620 device integrates a Arm® Cortex® A55 DSU sub-system as the SoC CPU.

#### 3.1. Cortex A55 DSU Sub-system

Figure 5 is a CPU block diagram.

Figure 5. Cortex-A55 DSU Block Diagram

The Cortex-A55 DSU sub-system integrates Arm DynamlQ Shared Unit (DSU) with Quad-Core Arm CortexA55 CPU, GIC, and the CoreSight™ components needed to debug the CPU.

The Cortex-A55 DSU sub-system consists of the following:

- Four Arm<sup>®</sup> Cortex<sup>®</sup>-A55 processors

- DSU that maintains coherency between the processors and arbitrates L3 requests from the processors

- One ACE host interface

- An APB Target interface for debug

The configuration options used for the implementation of the Cortex-A55 DSU sub-system are shown in Table 3.

Table 3. Cortex-A55 DSU Configuration Options

| Feature                                 | Option      |

|-----------------------------------------|-------------|

| Number of CA55 Processors               | 4           |

| Number of Interrupts                    | 0           |

| Integrated Generic Interrupt Controller | No          |

| L2 Cache Controller                     | Yes         |

| L1 Instruction Cache Size               | 32 KB       |

| L1 Data Cache Size                      | 32 KB       |

| L2 Cache Size                           | 64 KB       |

| L2 Data RAM Input Cycle Latency         | 1 cycle     |

| L2 Data RAM Output Cycle Latency        | 2 cycles    |

| L3 Cache                                | Yes         |

| L3 Cache Size                           | 512KB       |

| L3 Data RAM Input Cycle Latency         | 1 cycle     |

| L3 Data RAM Output Cycle Latency        | 2 cycles    |

| Trace For Each Processor                | Yes         |

| ROM APB Base Address                    | 22'h40_0000 |

| CPUO APB Debug Base Address             | 22'h40_4000 |

| CPU1 APB Debug Base Address             | 22'h40_5000 |

| CPU2 APB Debug Base Address             | 22'h40_6000 |

| CPU3 APB Debug Base Address             | 22'h40_7000 |

| Core 0 FPU                              | Yes         |

| Core 1 FPU                              | Yes         |

| Core 2 FPU                              | Yes         |

| Core 3 FPU                              | Yes         |

| Core 0 NEON <sup>™</sup> technology     | Yes         |

| Core 1 NEON <sup>™</sup> technology     | Yes         |

| Core 2 NEON <sup>™</sup> technology     | Yes         |

| Core 3 NEON <sup>™</sup> technology     | Yes         |

#### 3.2. Reference Documents

CPU users should be familiar with Arm documentation for these modules. Arm documentation is located at the Arm website: http://infocenter.arm.com.

Contact Arm support via email at: Support-cores@arm.com.

#### 3.3. Module Revision

Table 4 lists Arm revisions of modules used.

Table 4. ARM IP Revision

| Module        | Revision    |

|---------------|-------------|

| DSU           | r2p0-00rel0 |

| Arm CortexA55 | r4p0-00rel0 |

| CoreSight     | r1p0        |

#### 3.4. CPU Clock

The PLL provides the CortexA55 DSU sub-system clocks. The PLL can be programmed to a stable clock frequency from 20 MHz to 2 GHz. A specific sequence is required to change the PLL frequency.

#### 4. Boot ROM

#### 4.1. Overview

The SL1620 device ROM boot flow, the layout of the flash image, and secure boot scheme are described in this chapter.

The related hardware modules are as follows:

- Boot strap

- SoC CPU

- eMMC Controller

- SPI Controller

- USB Controller

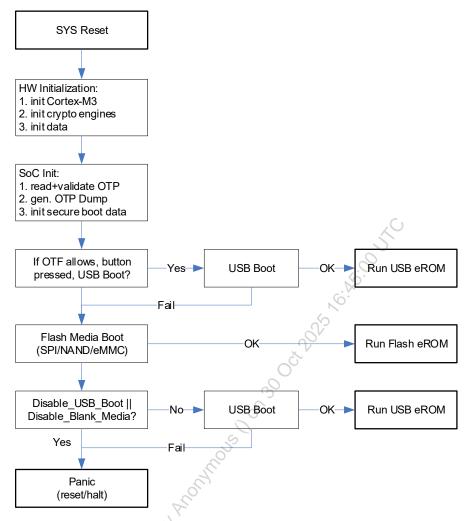

#### 4.2. SL1620 ROM Code Flow

The SL1620 device can boot in the following different scenarios depending on the boot strap options:

- SPI-Secure-The SoC boots from iROM and loads an encrypted image from SPI flash; upon decryption and security verification, the decrypted image takes control of CPU for the remainder of boot up.

- eMMC-Secure-The SoC boots from iROM and loads an encrypted image from eMMC flash; upon decryption and security verification, the decrypted image takes control of the CPU for the remainder of boot-up.

- USB-Secure-Conditionally supported based on OTP field. The SoC boots from iROM and loads an encrypted signed image from the USB host; upon decryption and security verification, the decrypted image takes control of the CPU for the remainder of boot up.

The same ROM code is used for SPI-Secure and eMMC-Secure boot options; the iROM code is executed in the Secure Processor (SCPU; the Arm Cortex M3) domain. The iROM code loads the next stage extension of iROM (eROM) book image; the eROM is also executed in the SCPU and loads the Applications Processor (APCU. Arm Cortex 55) boot image (IM2) from one of the boot sources; decrypt and verify the IM2; then eROM starts the ACPU to execute IM2.

Figure 6 illustrates the iROM code flow.

Figure 6. ROM Code Flow

After boot up from iROM and eROM, the ACPU continues the boot flow with IM2 SPI or eMMC, or USB host. The boot flow of Image-2 is completely flexible and independent of the SL1620 device; therefore, it is not covered as part of this document.

The source of the eROM and the IM2 is determined by boot strap pins.

Table 5. SoC Boot Source

| Boot Up     | SW Strap0 | Boot Source<br>Strap[2] | Description                                          |

|-------------|-----------|-------------------------|------------------------------------------------------|

| SPI-Secure  | 0         | 00                      | Boot from iROM and load eROM and IM2 from SPI flash. |

| NAND-Secure | 0         | 01                      | Boot from iROM and load eROM and IM2 from NAND.      |

| eMMC-Secure | 0         | 10                      | Boot from iROM and load eROM and IM2 from eMMC.      |

| USB-Secure  | 1         | Xx                      | Boot from iROM and load eROM and IM2 from USB.       |

#### 4.3. Flash Layout

The flash has different layouts when the SoC boots from different sources.

#### 4.3.1. Multi-copies, Magic Number, and ECC Attributes in Page 0, Block 0

Page O stores the parameters. It is programmed once and is never changed. To be generic and simple, ECC is disabled when the iROM code reads Page O. One problem is that NAND flash can have read errors. Therefore, multiple copies must be stored to cover these errors.

Page 0 is fulfilled by the magic number and ECC attributes. In other words, for a 2K page size NAND flash, 256 copies are stored in Page 0; for 4K page size NAND flash, 512 copies are stored in Page 0.

The SL1620 ROM code can tolerate up to 127 bits for each 2K bytes.

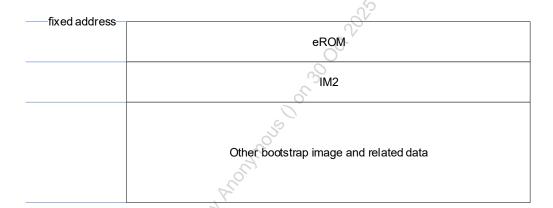

#### 4.3.2. SPI Flash for SPI-Secure Boot

The layout for SPI flash is shown in Figure 7. ROM code only reads Image-2 from the start of SPI flash (0xF000000) to SRAM. Figure 7 provides an example layout. The layout of another bootstrap image and related data is determined by IM2 and other designs (in other words, it can be changed and is not addressed in this document).

Figure 7. SPI Flash Layout for SPI-Secure Boot

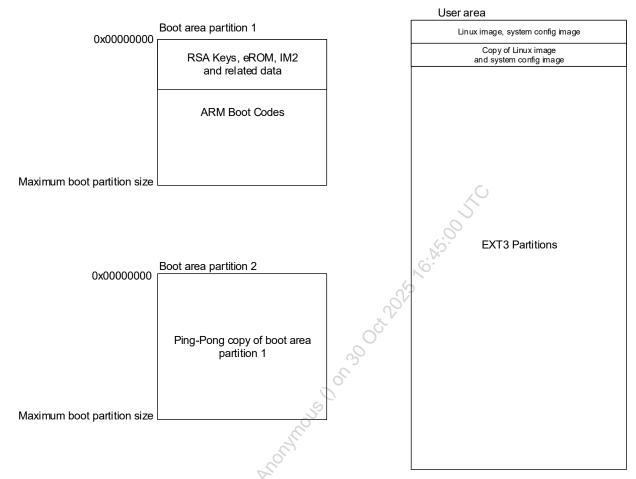

#### 4.3.3. eMMC Layout

#### 4.3.3.1.Partition Management in eMMC Device

The default area of the memory device consists of a User Data Area to store data, two possible boot area partitions for booting, and the Replay Protected Memory Block Area Partition to manage data in an authenticated and replay protected manner.

- Two Boot Area Partitions, whose size is multiple of 128 KB and from which booting from eMMC can be performed.

- Other user data area.

For other details about the eMMC partition management, refer to Section 7.2 and 7.3 in the *JEDEC STANDARD DESD84-A441*.

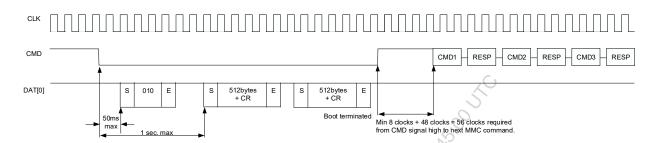

#### 4.3.4. Boot Operation Mode in eMMC

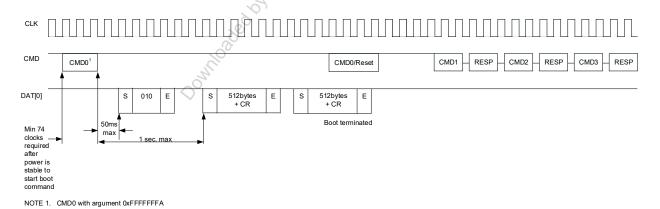

Based on eMMC standard, two boot operations are introduced.

Normal Boot operation (see section 7.3.3 in JEDEC STANDARD DESD84-A441)

If the CMD line is held Low for 74 clock cycles and more after power-up or reset operation (either through CMD0 with the argument of 0xF0F0F0F0 or assertion of hardware reset for eMMC, if it is enabled in Extended CSD register byte [162], bits [1:0]) before the first command is issued, the target recognizes that boot mode is being initiated and starts preparing boot data internally. The partition from which the host will read the boot data can be selected in advance using EXT\_CSD byte [179], bits [5:3].

The host can terminate boot mode with the CMD line High.

Figure 8 is the state diagram of boot mode.

Figure 8. State Diagram of Boot Mode

• Alternative boot operation (see section 7.3.4 in JEDEC STANDARD DESD84-A441)

This boot function is mandatory for device from v4.4 standard. After power-up or reset operation (either assertion of CMD0 with the argument of 0xF0F0F0F0 or hardware reset if it is enabled), if the host issues CMD0 with the argument of 0xFFFFFFA after 74 clock cycles, before CMD1 is issued or the CMD line goes Low, the target recognizes that boot mode is being initiated and starts preparing boot data internally. The partition from which the host reads the boot data can be selected in advance using EXT\_CSD byte [179], bits [5:3].

The host can terminate boot mode by issuing CMDO (Reset).

Figure 9 is the state diagram of alternative boot mode.

Figure 9. State Diagram of Alternative Boot Mode

#### 4.3.5. eMMC Boot in SL1620 Device

The SL1620 device supports alternative boot operation from the eMMC device (see Figure 10).

Figure 10. Layout of eMMC Device

Following are some inputs for the layout of eMMC boot:

- Two boot area partitions are defined as ping-pong copies; this ensures the system can boot if online upgrade fails.

- The iROM always tries to read eROM from the first boot area partition; if that attempt is not successful, the iROM reads eROM from the second boot area partition.

#### 4.3.6. eMMC Boot Mode

The SL1620 device does not support the primary boot mode but supports alternative boot mode. Therefore, the SL1620 cannot support the eMMC device which is compliant only with eMMC standard version 4.4.

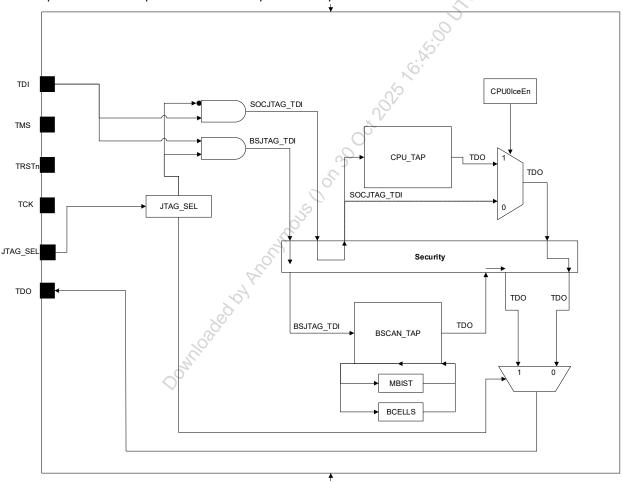

#### 5. JTAG

#### 5.1. Overview

The SL1620 device implements a standard IEEE 1149.1–compliant JTAG interface to support debugging of SOC\_CPU (ARM) through In–Circuit Emulation (ICE). Additionally, this JTAG interface is also used to control boundary scan (BSCAN) TAP controller, using which Memory Built–In Self Test (MBIST) and IJTAG paths are controlled.

#### 5.2. JTAG Debug Port Configurations

Figure 11 shows SL1620 JTAG chain connections for both ICE debugger and BSCAN mode. Both the BSCAN TAP controller and the ICE debugger share the same JTAG interface. To support security control features, either CPU ICE debugger interface or boundary scan access is disabled during power up. JTAG access protection level is provided by the OTP.

Figure 11. JTAG Chain and Boundary Scan diagram

JTAG\_SEL is used to select the BSCAN or ICE debugger path. JTAG\_SEL is from pad. For a secure ICE debugger, secure debug enable signal for the SOC\_CPU (drmCpuOlceEn) is generated by the security engine from siSS. Table 6 shows the different configurations of debug ports in the SL1620 device.

Table 6. SL1620 Debug Port Configuration

| {JTAG_SEL,<br>drmCpu0lceEn} | ENG_EN | BSCAN TAP | CPU TAP<br>(CoreSight™) |

|-----------------------------|--------|-----------|-------------------------|

| Ox                          | 1      | No        | Yes                     |

| 1x                          | 1      | Yes       | No                      |

| 01                          | 0      | No        | Yes                     |

| 00                          | 0      | No        | No                      |

| 1x                          | 0      | Yes       | No                      |

Note: {JTAG\_SEL,drmCpuOlceEn}=1x, and ENG\_EN = 0, secure access over JTAG to BSCAN\_TAP is controlled by other means.

#### 5.3. Boundary Scan Support

The SL1620 device supports the IEEE 1149.1-compliant boundary scan (BSCAN) interface. Table 7 is a list of instructions supported.

Table 7. SL1620 Supported Instructions

| Instruction    | Code       |  |

|----------------|------------|--|

| BYPASS         | 4'b1111    |  |

| EXTEST         | 4'b0001    |  |

| INTEST         | 4'b0100    |  |

| SAMPLE/PRELOAD | 4'b0101    |  |

| IDCODE         | 4'b1100    |  |

| HIGHZ          | 4'b0110    |  |

| CLAMP          | 4'b0000    |  |

| Reserved       | All others |  |

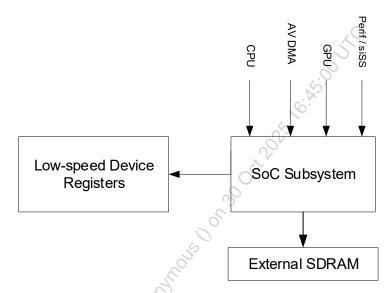

## 6. SoC Connectivity and Access Control

The main function of SoC subsystem is to link CPU and hardware engines with various targets, including DRAM, memory-mapped external Flash device, and an internal configuration bus. The destination of each transaction is decided solely on the transaction address. The SL1620 SoC subsystem handles 32-bit address space. Three targets are shared among the bus hosts, such as hardware DMA engines and CPUs. Simultaneous access to the same target from different hosts are arbitrated and sent to the addressed target in sequence. Accesses to different targets are independent and can be served concurrently. In addition to address-based routing, the SoC subsystem is also capable of protecting sensitive data content by rejecting untrusted transactions to DDR SDRAM or register spaces, including low-speed and fast-access registers.

Figure 12 shows the bus hosts and targets in the SL1620 device.

Figure 12. SL1620 Bus Hosts and Targets

#### 6.1. Connection Table

There are two transaction target regions in SL1620:

- DDR SDRAM memory

- o System memory

- Low-speed registers

- O Normal device registers running at 100 MHz

Possible hosts for these three targets are:

- CPU

- o Quad Arm CortexA55 core sub-system

- AV DMA

- O Direct-Memory Access engine fetching display video and audio output data and storing the video and audio input data.

- Peripheral DMAs

- Direct Memory Access engines for storing received data or loading transmitted data through various interfaces including USB2.0, USB3.0, Gigabit Ethernet, NAND flash, EMMC, SDIO

- Security Island Sub-System DMA

- GPU Engine

- o Storing or fetching graphic data

Table 8 shows the connection levels of various host and target pairs.

- Full means the host can access full range of target without constraint.

- No Access means there is no logical connection for the host/target pair.

Table 8. Host and Target Pair Connection Levels

| Targets             | DDR SDRAM  | Fast-Access<br>Registers | Low-Speed<br>Registers |

|---------------------|------------|--------------------------|------------------------|

| Hosts               | DDR 3DRAIM |                          |                        |

| CPU                 | Full       | Full                     | Full                   |

| AV DMA engine       | Full       | No Access                | No Access              |

| Perif DMA           | Full       | Full                     | Full                   |

| Security Island DMA | Full       | Full                     | Full                   |

| GPU                 | Full       | No Access                | No Access              |

#### 6.1.1. Address Map

Table 9. System Memory Map

| Address Range                 | Host CPU         | USB/GE/eMMC/SDIO | All Other DMAs |

|-------------------------------|------------------|------------------|----------------|

| 0x0000000000 ~<br>0x0DFFFFFF  | DDR<br>(0~3.5GB) | DDR<br>(0~3.5GB) |                |

| 0x0F00000000 ~<br>0x0F1FFFFFF | SPI              | SPI              | DDR<br>(0~4GB) |

| 0x0F20000000 ~<br>0x0FFFFFFF  | Register         | Register         |                |

Table 10. Low-Speed Register Memory Map

|                                    | Address Range in Hexadecimal | Size      |

|------------------------------------|------------------------------|-----------|

| SPI Flash                          | 0xF000_0000 ~ 0xF1FF_FFFF    | 32MByte   |

| CoreSight Registers                | 0xF680_0000 ~ 0xF6FF_FFFF    | 8MByte    |

| Encoder Registers                  | 0xF700_0000 ~ 0xF700_0FFF    | 4MByte    |

| AVIO Registers                     | 0xF740_0000 ~ 0xF75F_FFFF    | 2MByte    |

| GIC400 Registers                   | 0xF790_0000 ~ 0xF790_7FFF    | 32MByte   |

| CPU Registers                      | 0xF792_0000 ~ 0xF792_FFFF    | 64KByte   |

| MCtrl Subsystem Registers          | 0xF794_0000 ~ 0xF794_FFFF    | 64Kbyte   |

| GPU Registers                      | 0xF798_0000 ~ 0xF79F_FFFF    | 512Kbytes |

| EMMC Registers                     | 0xF7AA_0000 ~ 0xF7AA_0FFF    | 4Kbyte    |

| SDIO3.0 Controller Registers       | OxF7AB_OOOO ~ OxF7AB_OFFF    | 9 4Kbyte  |

| PBRIDGE Registers                  | 0xF7B3_0000 ~ 0xF7B3_FFFF    | 64Kbyte   |

| MTEST Registers                    | 0xF7B4_0000 ~ 0xF7B4_FFFF    | 64Kbyte   |

| Gigabit Ethernet Registers         | 0xF7B6_0000 ~ 0xF7B6_FFFF    | 64Kbyte   |

| USB2.0 OTG Controller<br>Registers | 0xF7C0_0000 ~ 0xF7C7_FFFF    | 512Kbyte  |

| SoC Registers                      | 0xF7CA_0000 ~ 0xF7CA_FFFF    | 64Kbyte   |

| Memory Controller Registers        | 0xF7CB_0000 ~ 0xF7CB_3FFF    | 16Kbyte   |

| USB3 Registers                     | 0xF7D0_0000 ~ 0xF7DF_FFFF    | 1MB       |

| ApbPerif Registers                 | 0xF7E8_0000 ~ 0xF7E8_FFFF    | 64Kbyte   |

| Chip Control Registers             | OxF7EA_0000 ~ OxF7EA_FFFF    | 64Kbyte   |

| NAND Target DMA                    | 0xF7F0_0000 ~ 0xF7F0_FFFF    | 64Kbyte   |

| NAND AHB Registers                 | 0xF7F1_0000 ~ 0xF7F1_FFFF    | 64Kbyte   |

| Pulse Width Modulator<br>Registers | 0xF7F2_0000 ~ 0xF7F2_FFFF    | 64Kbyte   |

| MC DFIO Control Registers          | 0xF800_0000 ~ 0xF800_0FFF    | 4MB       |

| MPTS Registers                     | 0xF900_0000 ~ 0xF903_FFFF    | 256Kbyte  |

| Boot-Vector                        | OxFFFF_0000 ~ OxFFFF_FFFF    | 64Kbyte   |

# 7. Security Island Subsystem

#### 7.1. Overview

SISS has an OTP main block.

#### 7.2. OTP

Functions included in this core are:

- 32K bits OTP using anti-fuse technology

- Un-programmed value of OTP bit is zero, programmed value is zero/one

- Built-in charge pump to provide programming power

- Built-in programming sequencer with (SMART programming algorithm)

- Synchronous OTP interface (x16 bit for read, x1 bit for program)

- Simplified interface for reading, programming and manufacturing test operations

- BIST (built-in self-test) to cover:

- o Bit and word line integrity (TESTDEC) of memory array

- O Gate oxide integrity (Blank Check) of memory array

- o Test programming (WRTEST) of spare memory

- Repair of failing banks for 100% Blank Check manufacturing yield

The OTP provides a synchronous, 16-bit-wide read-bus interface reading and a synchronous, 1-bit wide bus interface for programming.

## 8. DDR Memory Controller

#### 8.1. Introduction

The SL1620 memory controller receives transactions from the SoC core. These transactions are queued internally and scheduled for access to the SDRAM while satisfying the SDRAM protocol timing requirements, transaction priorities, and dependencies between the transactions. The memory controller in turn issues commands on the DFI interface to the PHY module, which launches and captures data to and from the SDRAM.

The SL1620 memory controller is designed for ARM AXI bus protocols. It has two generic ports for different hosts in the SoC. Along with built-in arbitration schemes, it also acts as a bus fabric and reduces the size and latency of the AXI fabric.

#### 8.2. Memory Controller Feature List

- DDR PHY Interface (DFI) support for easy integration with industry standard DFI 3.1-compliant PHYs.

- X32 DRAM Bus Width support.

- DDR3 support.

- Direct software request control or programmable internal control for ZQ short calibration cycles.

- Support for ZQ long calibration after self-refresh exit.

- Dynamic scheduling to optimize bandwidth and latency.

- Read and write buffers in fully associative CAMs, configurable in powers of two, from 16 up to 64 reads and 64 writes.

- Delayed writes for optimum performance on SDRAM data bus.

- For maximum SDRAM efficiency, commands are executed out-of-order:

- o Read requests accompanied by a unique token (tag) from HIF.

- Read data returned with token (tag) for SoC core to associate read data with correct read request.

- Hardware configurable and software programmable Quality of Service (QoS) support:

- O For three traffic classes on read commands-high priority reads, variable priority reads, and low priority reads.

- O For two traffic classes on write commands-normal priority writes and variable priority writes.

- o For port urgent and port throttling control.

- If QOS support is not configured in the hardware:

- o Two traffic classes on read commands-high priority reads and low priority reads.

- O One traffic class on write commands-normal priority writes.

- Programmable SDRAM parameters.

- Configurable maximum SDRAM data-bus width (denoted as "full data-bus width" below).

- Programmable support for all the following SDRAM data-bus widths:

- o Full data-bus width, or

- o Half of the full data-bus width.

- Guaranteed coherency for write-after-read (WAR) and read-after-write (RAW) hazards.

- Write combine to allow multiple writes to the same address to be combined into a single write to SDRAM; supported for same starting address.

- Paging policy selectable by configuration registers as any of the following:

- O Leave pages open after accesses, or

- Close page when there are no further accesses available in the controller for that page, or

- O Auto-precharge with each access, with an optimization for page-close mode which leaves the page open after a flush for read-write and write-read collision cases.

- Supports automatic SDRAM power-down entry and exit caused by lack of transaction arrival for a programmable time.

- Supports self-refresh entry and exit.

- Support for dynamically changing clock frequency while in self-refresh.

- Leverages out of order requests with CAM to maximize throughput.

- APB interface for the memory controller software accessible registers.

- Compatibility with the AMBA 4 AXI4 and AMBA 3 AXI protocols.

- Read reorder buffer with reduced latency options.

#### 8.3. DDR Memory Controller Overview

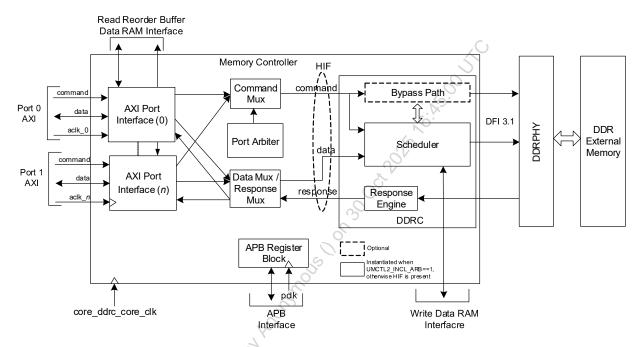

Figure 13. DDR Memory Controller Top-Level Block Diagram

The memory controller contains the following main architectural components:

- The AXI Port Interface (XPI) block: This block provides the interface to the application ports. It provides bus protocol handling, data buffering and reordering for read data, data bus size conversion (up-sizing or downsizing), and memory burst address alignment. Read data is stored in a SRAM, read re-order buffer and returned in order, to the AXI ports. The SRAM may be instantiated as embedded memory external to the memory controller or implemented as flops within the memory controller.

- The Port Arbiter (PA) block: This block provides latency sensitive, priority-based arbitration between the addresses issued by the XPIs (by the ports).

- The DDR Controller (DDRC) block: This block contains a logical CAM (Content Addressable Memory), which can be synthesized using standard cells. This holds information on the commands, which is used by the scheduling algorithms to optimally schedule commands to be sent to the PHY, based on priority, bank/rank status and DDR timing constraints. A bypass path is also provided.

- The APB Register block: This block contains the software accessible registers.

#### 8.4. Functional Description

The memory controller performs the following functions:

- Accepts requests from the SoC core with system addresses and associated data for writes.

- Performs address mapping from system addresses to SDRAM addresses (rank, bank, bank group, row).

- Prioritizes requests to minimize the latency of reads (especially high priority reads) and maximize page hits.

- Ensures that the SDRAM is properly initialized.

- Ensures that all requests made to the SDRAM are legal (accounting for associated SDRAM constraints).

- Ensures that refreshes and other SDRAM and PHY maintenance requests are inserted as required.

- Controls when the SDRAM enters and exits the various power-saving modes appropriately.

#### 8.5. DDR PHY Overview

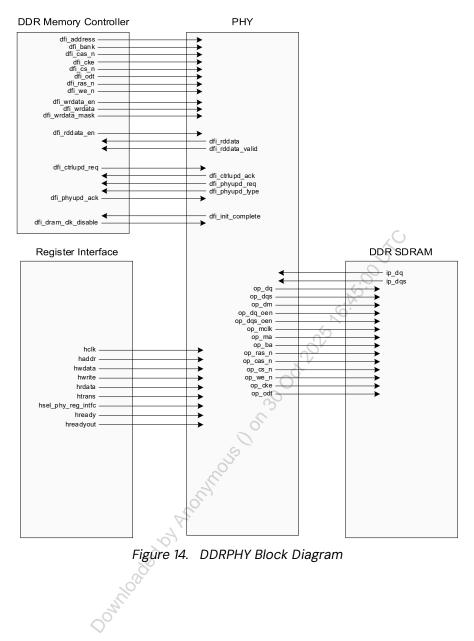

DDRPHY is an implementation of DFI4.0 specification that describes the inter-operation between a DDR memory controller and the physical interface (PHY).

# 9. Graphics Engine

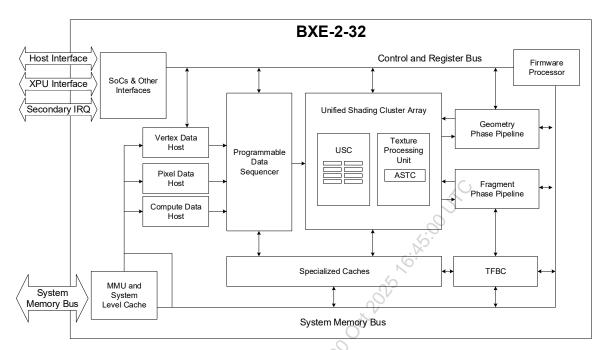

The Imagination™ graphics processing IP, included within the SL1620 SoC, is defined as a family of high-performance GPU cores that deliver hardware acceleration for 3D graphics displays for next generation IoT devices.

The IMG B-Series BXE-2-32 core is a reusable IP block designed to bring high quality graphics acceleration and GPU compute capability to System-on-Chip (SoC) designs for a wide range of target applications; for example, smart home and appliances, security, streaming, mobile computing and control systems.

### 9.1. GPU Features and Supported Standards

### 9.1.1. GPU Key Features

The Imagination B-Series graphics processors are built around multi-threaded Unified Shading Clusters (USCs) which feature an ALU architecture with high SIMD efficiency, and support tile-based deferred rendering with concurrent processing of multiple tiles.

The B-Series core has the following features:

- Base architecture, fully compliant with the following APIs:

- o OpenGL® ES™ 3.2

- o EGL 1.4

- o OpenCL™ 1.2EP

- o Vulkan® 1.2

- o Android™ NN HAL

- Tile-based deferred rendering architecture for 3D graphics workloads, with concurrent processing of multiple tiles.

- Programmable high quality image anti-aliasing.

- Fine grain triangle culling.

- Support for DRM security.

- Support for GPU virtualization

- O Up to 8 virtual GPUs

- o Support for IMG hyper-lane technology, with 8 hyper-lanes available

- o Separate IRQs per OSID

- Multi-threaded Unified Shading Cluster (USC) engine incorporating pixel shader, vertex shader and GP- GPU (compute shader) functionality.

- USC incorporates an ALU architecture with high SIMD efficiency.

- Fully virtualized memory addressing (up to 64 GB address space), supporting unified memory architecture.

- Fine-grained task switching, workload balancing and power management.

- Advanced DMA driven operation for minimum host CPU interaction.

- System Level Cache (SLC).

- o The size of the SLC can be configured by the customer

- Specialized Texture Cache Unit (TCU).

- Compressed Texture decoding.

- Lossless and/or visually lossless low area image compression the Imagination frame buffer compression and decompression (TFBC) algorithm

- Dedicated processor for B-Series core firmware execution.

- o Single-threaded firmware processor with a 2KB instruction cache and a 2KB data cache.

- Separate power island for the firmware processor

- On-Chip Performance, Power, and Statistics Registers.

### 9.1.2. Unified Shading Cluster Features

- Number of ALU pipelines: 2.

- 8 parallel instances per clock.

- Local data, texture and instruction caches.

- Variable length instruction set encoding.

- Full support for OpenCL™ atomic operations.

- Scalar and vector SIMD execution model.

- USC F16 Sum-of-Products Multiply-Add (SOPMAD) Arithmetic Logic Unit (ALU).

### 9.1.3. 3D Graphics Features

- Rasterization

- o Deferred Pixel Shading.

- o On-chip tile floating point depth buffer.

- 0 8-bit stencil with on-chip tile stencil buffer.

- o Maximum tiles in flight (per ISP): 2.

- o 16 parallel depth/stencil tests per clock.

- o 1 fixed-function rasterization pipeline(s).

- Texture Lookups

- O Load from source instruction support.

- o Texture writes enabled through the Texture Processing Unit.

- Filtering

- o Point, bilinear and tri-linear filtering.

- o Anisotropic filtering.

- O Corner filtering support for Cube Environment Mapped textures and filtering across faces.

- Texture Formats

- o ASTC LDR compressed texture format support.

- TFBC lossless and/or lossy compression format support for non-compressed textures and YUV textures.

- o ETC

- o YUV planar support.

- Resolution Support

- o Frame buffer max size = 8K × 8K

- o Texture max size = 8K × 8K.

- Anti-aliasing

- o Maximum 4× multi-sampling.

- Primitive Assembly

- o Early hidden object removal.

- o Tile acceleration.

- Render to Buffers

- o Twiddled format support

- Multiple on-chip render targets (MRT)

- o Lossless and/or lossy Frame Buffer Compression (and Decompression)

- O Programmable Geometry Shader Support

- o Direct Geometry Stream Out (Transform Feedback)

### 9.1.4. Compute Features

- 1, 2, and 3-dimensional compute primitives.

- Block DMA to/from USC Common Store (for local data).

- Per task input data DMA (to USC Unified Store).

- Conditional execution.

- Execution fences.

- Compute workload can be overlapped with any other workload.

- Round to nearest even.

#### 9.1.5. TFBC Features

- Lossless delta encoding algorithm

- Multiple levels of lossy compression, with memory footprint reduction to 75%, 50% or 25% of the original data size

- O Lossy compression reduces memory bandwidth

- Block size is 64 x 32-bit pixels, these can be 8 x 8 or 16 x 4 in shape

- Throughput up to 4 pixels of 4 × 8 bits each per clock (4 pixels × 4 channels × 8 bits)

- No increase in data size.

- Formats: 1, 2, 3 or 4 channels of U8, U16, U32, F16, or F32 (up to 4 components). Max pixel size is 32 bits

- Per plane YUV planar (2 or 3 plane) video compression.

# 9.2. GPU Integration Overview

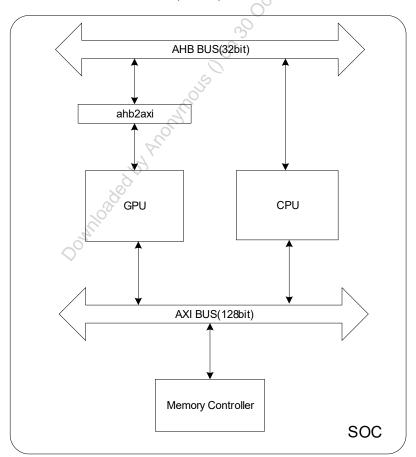

Figure 15 shows the view of BXE-2-32 core in the Synaptics SoC. The BXE-2-32 (GPU) core and Host CPU work together to process the various workloads that are supported by the BXE-2-32 core, while the BXE-2-32 core needs access to a memory subsystem to fetch commands and data.

Figure 15. BXE-2-32 core in SoC

The SoC interconnect, or bus fabric, as shown in the Figure 15, consists of two key buses:

- Memory interconnect to allow the SoC modules access to system memory (for example, SDRAM, FLASH, and so on) via the memory controller.

- System bus to allow a host CPU to access configuration/status registers of various target IPs in the SoC, such as the BXE-2-32 core.

Dominos de la Arroma de la Arro

### 9.3. GPU Bus Interface

This section describes the bus interface groups for an AXI bus protocol configured BXE-2-32 core. There are two bus interface groups in the BXE-2-32 design, the system bus interface and the memory bus interface. Each group is independent of the other in terms of the bus width and how they can operate.

### 9.3.1. AXI Host Interface

This is an AXI host interface (AXI MEMIF). It consists of a single channel denoted as O. A channel is a 128-bit wide port and is used to read and write the memory data from/to memory. The mapping of physical addresses generated from the core to the port is configurable according to BXE-2-32 configuration registers.

Table 11. Features of GPU AXI Host Interface

| Feature                                         | Characteristic                                                                                                                            |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Number of memory interfaces                     | 1                                                                                                                                         |

| Allowable Bus / Core Clock Relationship         | Asynchronous Interface                                                                                                                    |

| Related to clock                                | mem_clk                                                                                                                                   |

| AXI type                                        | ACE Lite                                                                                                                                  |

| Host or Target                                  | Host                                                                                                                                      |

| Burst attribute                                 | Max Burst: 4 beats Incrementing (wrapped burst type is not supported)                                                                     |

| Burst size                                      | Total max burst is 64 bytes which equals:<br>128 bits * 4(burst size * burst length)                                                      |

| Address bus width                               | 36 bits                                                                                                                                   |

| Data bus width                                  | 128 bits                                                                                                                                  |

| Tag ID width                                    | 6 bits                                                                                                                                    |

| Number of IDs                                   | 2 <sup>6</sup>                                                                                                                            |

| Max number of outstanding reads                 | 64                                                                                                                                        |

| Max number of outstanding writes                | 64                                                                                                                                        |

| Combined number of outstanding reads and writes | 96 combined read <i>and</i> write transactions. The total number of outstanding tag IDs can be any mix of read and write at any one time. |

| Interleaving                                    | Write Interleaving is not supported                                                                                                       |

| Sideband signals                                | AXI_AxUSER_MEMIF: Bit 5:O - Internal Tag ID Bits 8:6 - OSID Bit 9 - FW Code Access Bit 10 - Trusted Access                                |

### 9.3.2. AXI SoC Interface

The SoC Interface (SOCIF) is an AXI Target interface. This interface is used to access the BXE-2-32 control registers. It is a fixed 32-bit data interface.

The SOCIF interface tag width is configurable and specified by the generic AXI\_SOCIF\_TAG\_WIDTH.

The interface supports write byte masking and the byte mask does not apply to read accesses. This is so that only writes which the driver intends to make into the device are observed irrespective of the bus width. Fully masked writes to the SoC Interface are supported.

Table 12. Features of GPU AXI SoC Interface

| Feature                                 | Characteristic                        |

|-----------------------------------------|---------------------------------------|

| Allowable Bus / Core Clock Relationship | Asynchronous Interface                |

| Related to clock                        | sys_clk                               |

| AXI type                                | AXI3                                  |

| Host or Target                          | Target                                |

| Burst attribute                         | Bursts are not supported on the SOCIF |

| Address bus width                       | 32 bits                               |

| Data bus width                          | 32 bits                               |

| Tag ID width                            | 10 bits                               |

| Number of IDs                           | 210                                   |

| Max number of outstanding reads         | 4                                     |

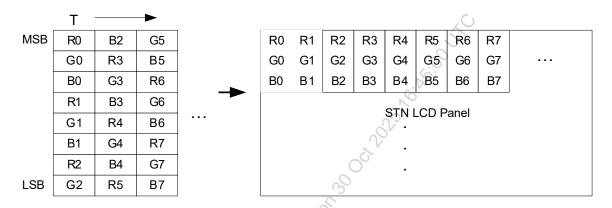

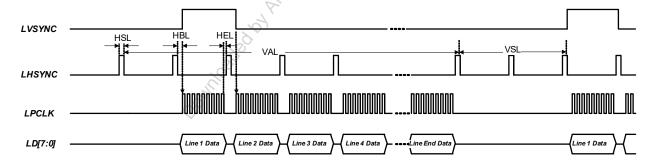

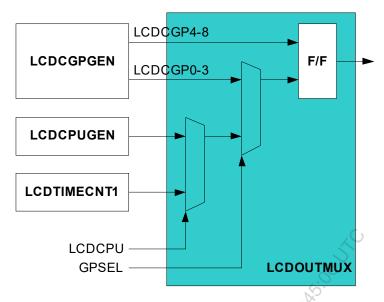

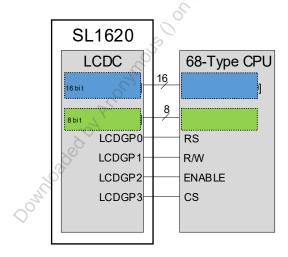

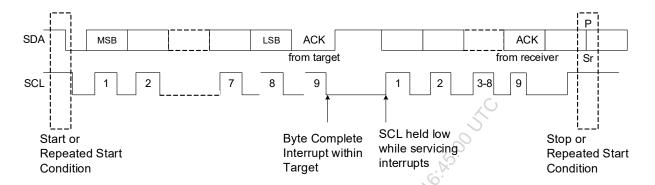

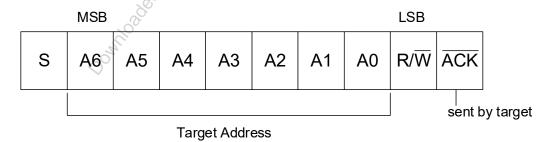

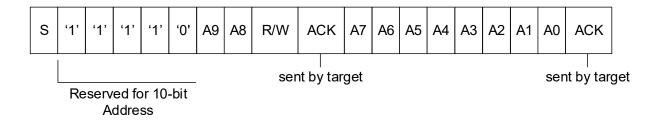

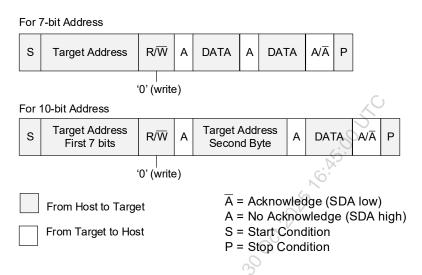

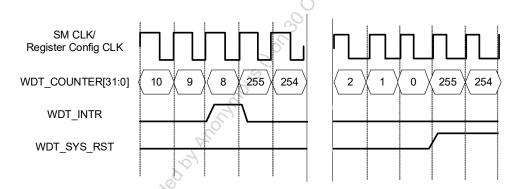

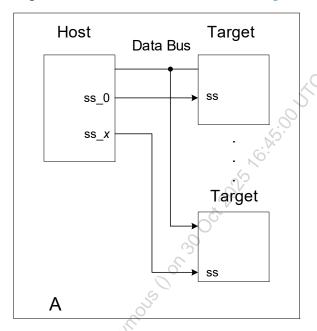

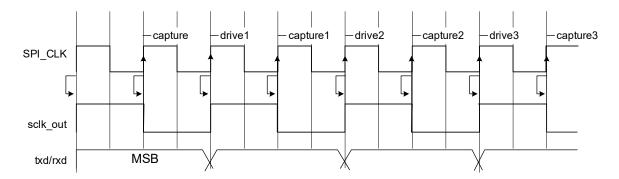

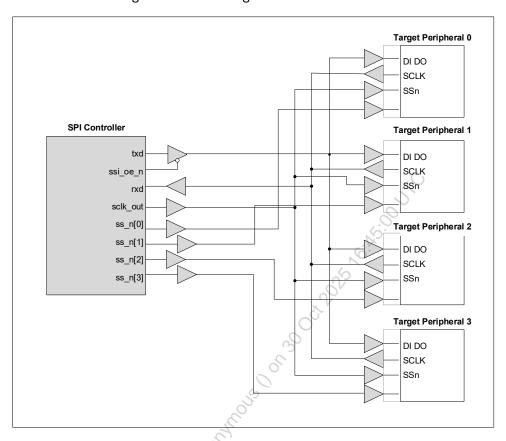

| Max number of outstanding writes        | 4                                     |